- 您现在的位置:买卖IC网 > PDF目录15524 > ISL8118IRZ (Intersil)IC REG CTRLR BUCK PWM VM 28-QFN PDF资料下载

参数资料

| 型号: | ISL8118IRZ |

| 厂商: | Intersil |

| 文件页数: | 11/20页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM VM 28-QFN |

| 标准包装: | 60 |

| PWM 型: | 电压模式 |

| 输出数: | 1 |

| 频率 - 最大: | 2MHz |

| 占空比: | 100% |

| 电源电压: | 2.97 V ~ 22 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 28-VFQFN 裸露焊盘 |

| 包装: | 管件 |

| 产品目录页面: | 1244 (CN2011-ZH PDF) |

�� �

�

�

�ISL8118�

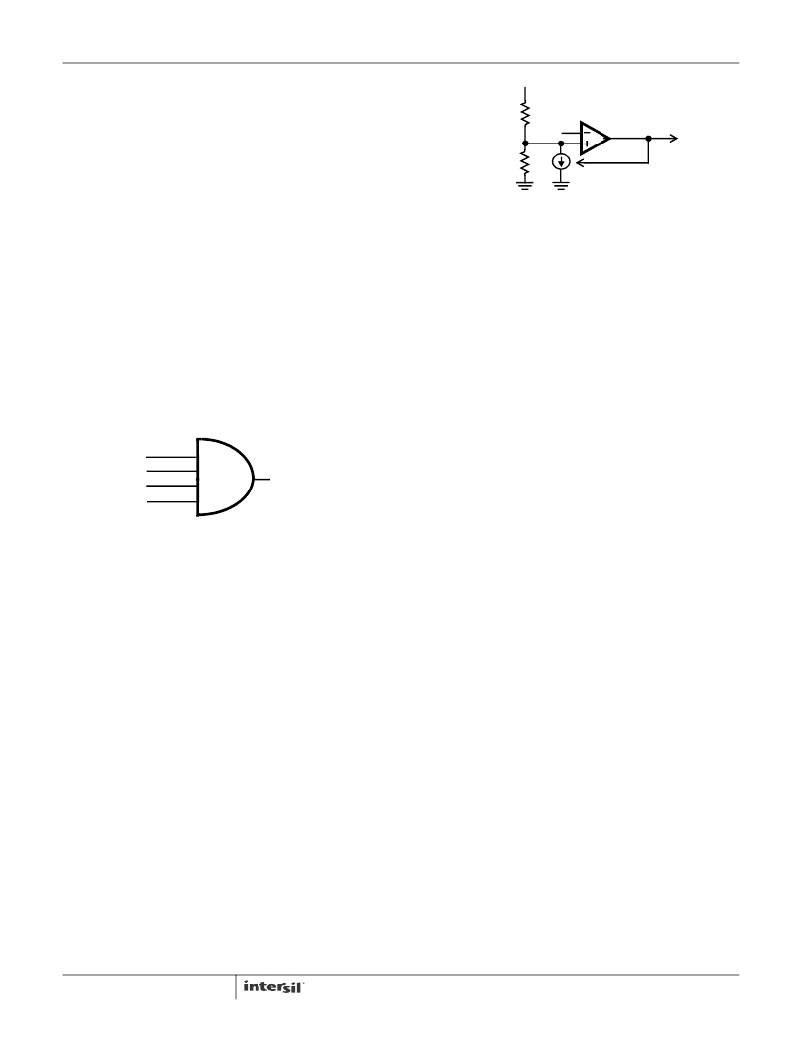

�OV/UV/PGOOD� comparators.� The� VDIFF� pin� should� be�

�connected� to� the� FB� pin� by� a� standard� feedback� network.� In�

�VIN�

�the� event� that� the� remote� sense� buffer� is� disabled,� the� VDIFF�

�pin� should� be� connected� to� VOUT� by� a� resistor� divider� along�

�R� UP�

�V� REF�

�Sys_Enable�

�with� FB’s� compensation� network.� An� RC� filter� should� be� used�

�R� UP� =� --------------------------�

�R� DOWN� =� ---------------------------------------------------------�

�if� VDIFF� is� to� be� connected� directly� to� FB� instead� of� to� VOUT�

�through� a� separate� resistor� divider� network.�

�GND� (Bottom� Side� Pad,� Analog� Ground)�

�Signal� ground� for� the� IC.� All� voltage� levels� are� measured�

�with� respect� to� this� pin.� This� pin� should� not� be� left� floating.�

�Functional� Description�

�Initialization�

�The� ISL8118� automatically� initializes� upon� receipt� of� power�

�without� requiring� any� special� sequencing� of� the� input�

�supplies.� The� Power-On� Reset� (POR)� function� continually�

�monitors� the� input� supply� voltages� (PVCC,VFF,� VCC)� and�

�the� voltage� at� the� EN� pin.� Assuming� the� EN� pin� is� pulled� to�

�above� ~0.50V,� the� POR� function� initiates� soft-start� operation�

�after� all� input� supplies� exceed� their� POR� thresholds.�

�HIGH� =� ABOVE� POR;� LOW� =� BELOW� POR�

�VCC� POR�

�R� DOWN�

�I� EN_HYS� =� 10μA�

�V� EN_HYS�

�I� EN_HYS�

�R� UP� ?� V� EN_REF�

�V� EN_FTH� –� V� EN_REF�

�V� EN_FTH� =� V� EN_RTH� –� V� EN_HYS�

�FIGURE� 2.� ENABLE� POR� CIRCUIT�

�Soft-start�

�The� POR� function� activates� the� internal� 38μA� OTA� which�

�begins� charging� the� external� capacitor� (C� SS� )� on� the� SS� pin� to� a�

�target� voltage� of� VCC.� The� ISL8118’s� soft-start� logic� continues�

�to� charge� the� SS� pin� until� the� voltage� on� COMP� exceeds� the�

�bottom� of� the� oscillator� ramp,� at� which� point,� the� driver� outputs�

�are� enabled,� with� the� bottom� side� MOSFET� first� being� held� low�

�for� 200ns� to� provide� for� charging� of� the� bootstrap� capacitor.�

�Once� the� driver� outputs� are� enabled,� the� OTA’s� target� voltage� is�

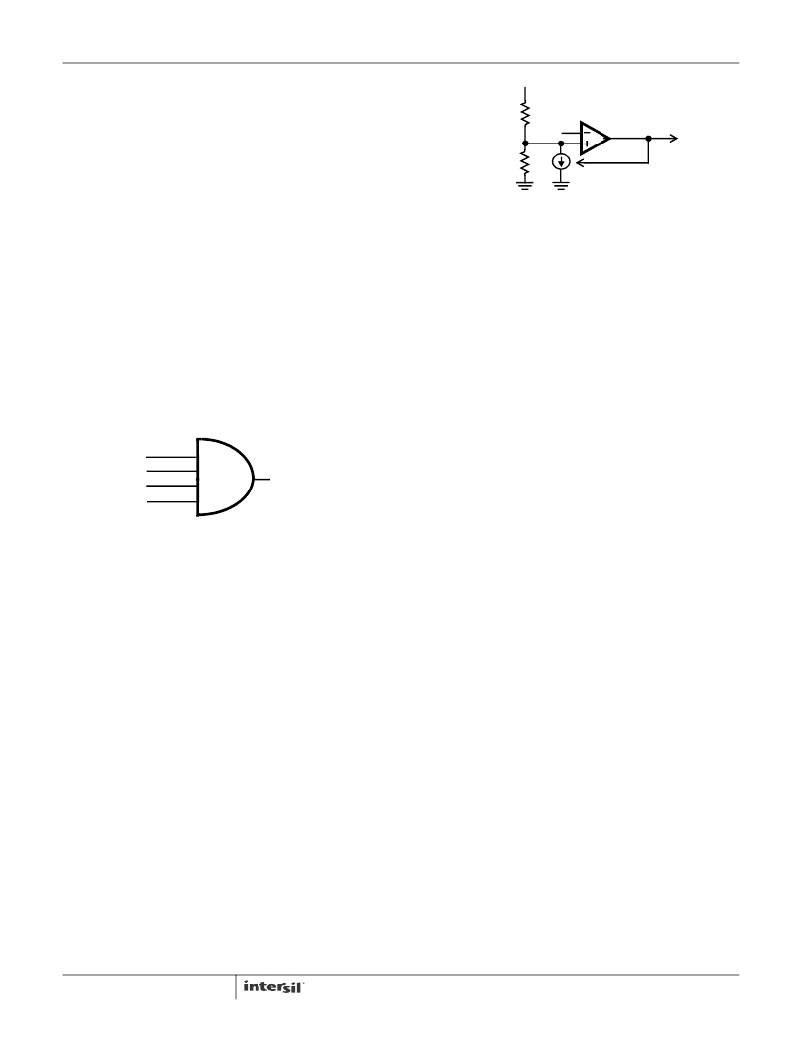

�VFF� POR�

�PVCC� POR�

�EN� POR�

�AND�

�SOFT-START�

�then� changed� to� the� margined� (if� margining� is� being� used)�

�reference� voltage� (V� REF_MARG� ),� and� the� SS� pin� is� ramped� up�

�or� down� accordingly.� This� method� reduces� start-up� surge�

�currents� due� to� a� pre-charged� output� by� inhibiting� regulator�

�FIGURE� 1.� SOFT-START� INITIALIZATION� LOGIC�

�With� all� input� supplies� above� their� POR� thresholds,� driving�

�the� EN� pin� above� 0.50V� initiates� a� soft-start� cycle.� In� addition�

�to� normal� TTL� logic,� the� enable� pin� can� be� used� as� a� voltage�

�monitor� with� programmable� hysteresis� through� the� use� of� the�

�internal� 10mA� sink� current� and� an� external� resistor� divider.�

�This� feature� is� especially� designed� for� applications� that� have�

�input� rails� greater� than� a� 3.3V� and� require� specific� input� rail�

�POR� and� Hysteresis� levels� for� better� undervoltage�

�protection.� Consider� for� a� 12V� application� choosing�

�RUP� =� 100k� Ω� and� RDOWN� =� 5.76k� Ω� there� by� setting� the�

�rising� threshold� (VEN_RTH)� to� 10V� and� the� falling� threshold�

�(VEN_FTH)� to� 9V,� for� 1V� of� hysteresis� (VEN_HYS).� Care�

�should� be� taken� to� prevent� the� voltage� at� the� EN� pin� from�

�exceeding� VCC� when� using� the� programmable� UVLO�

�functionality.�

�11�

�switching� until� the� control� loop� enters� its� linear� region.� By�

�ramping� the� positive� input� of� the� error� amplifier� to� VCC� and�

�then� to� V� REF_MARG� ,� it� is� even� possible� to� mitigate� surge�

�currents� from� outputs� that� are� pre-charged� above� the� set� output�

�voltage.� As� the� SS� pin� connects� directly� to� the� non-inverting�

�input� of� the� Error� Amplifier,� noise� on� this� pin� should� be� kept� to� a�

�minimum� through� careful� routing� and� part� placement.� To�

�prevent� noise� injection� into� the� error� amplifier,� the� SS� capacitor�

�should� be� located� within� 150� mils� of� the� SS� and� GND� pins.�

�Soft-start� is� declared� done� when� the� drivers� have� been� enabled�

�and� the� SS� pin� is� within� ±3mV� of� V� REF_MARG� .�

�Power� Good�

�The� power� good� comparator� references� the� voltage� on� the�

�soft-start� pin� to� prevent� accidental� tripping� during� margining.�

�The� trip� points� are� shown� on� Figure� 3.� Additionally,� power�

�good� will� not� be� asserted� until� after� the� completion� of� the�

�soft-start� cycle.� A� 0.1μF� capacitor� at� the� PGDLY� pin� will� add�

�an� additional� ~7.1ms� delay� to� the� assertion� of� power� good.�

�PGDLY� does� not� delay� the� deassertion� of� power� good.�

�FN6325.2�

�November� 29,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL8130IRZ | IC REG CTRLR BST FLYBK PWM 20QFN |

| ADZS-BF537-ASKIT | BOARD EVAL SKIT ADSP-BF537 |

| ECC18DRAS | CONN EDGECARD 36POS R/A .100 SLD |

| V300C36C75BF | CONVERTER MOD DC/DC 36V 75W |

| SEK100M250ST | CAP ALUM 10UF 250V 20% RADIAL |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL8118IRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 28-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8120 | 制造商:INTERSIL 制造商全称:Intersil Corporation 功能描述:Dual/n-Phase Buck PWM Controller with Integrated Drivers |

| ISL8120CRZ | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8120CRZ-T | 功能描述:IC REG CTRLR BUCK PWM VM 32-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL8120CRZ-TS2568 | 制造商:Intersil Corporation 功能描述:INTEL, ISL8120CRZ-T W/BARCODE LABELS, 12 MONTH D/C RESTRICTI - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。