- 您现在的位置:买卖IC网 > PDF目录20665 > ISL8723EVAL1 (Intersil)EVAL BOARD 1 FOR ISL8723 PDF资料下载

参数资料

| 型号: | ISL8723EVAL1 |

| 厂商: | Intersil |

| 文件页数: | 5/14页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD 1 FOR ISL8723 |

| 产品培训模块: | Solutions for Industrial Control Applications |

| 标准包装: | 1 |

| 系列: | * |

�� �

�

�

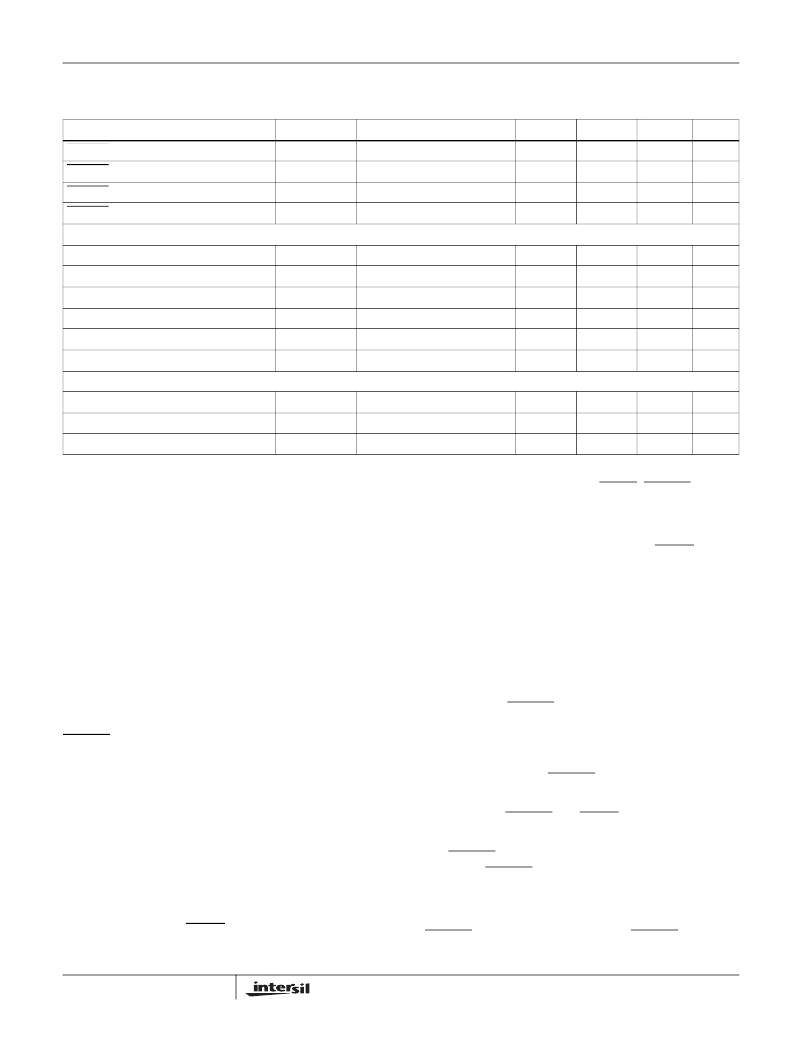

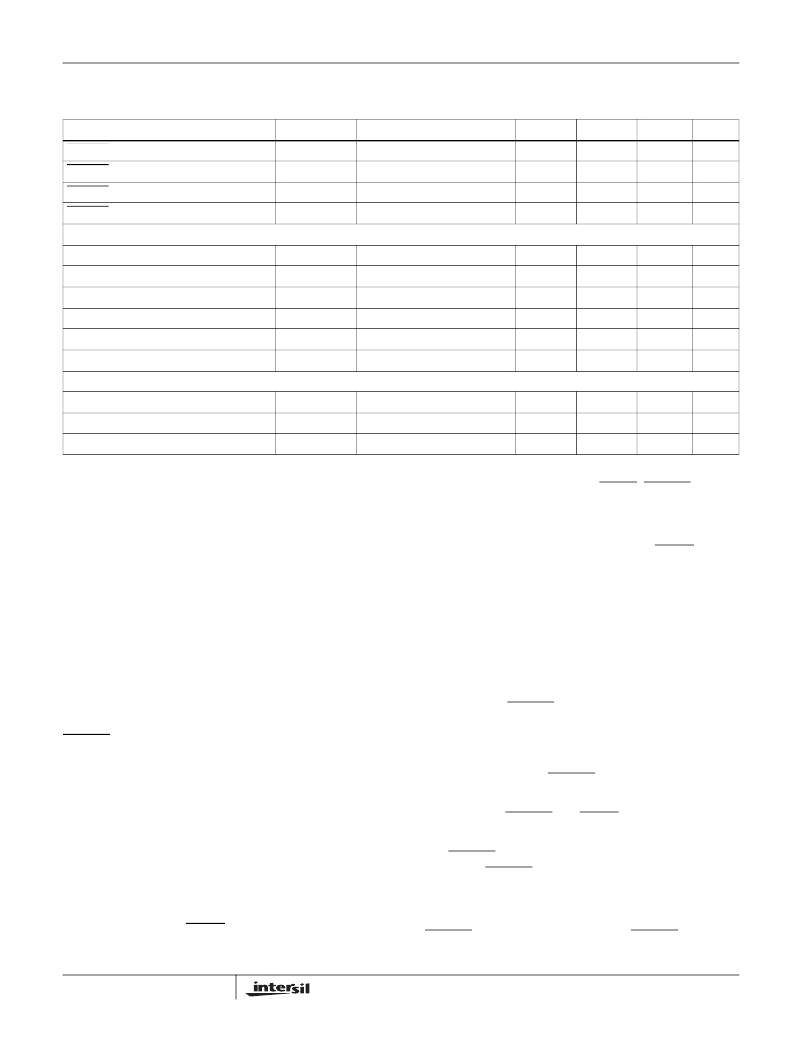

�ISL8723,� ISL8724�

�Electrical� Specifications�

�V� DD� =� 3.3V� to� +5V,� T� A� =� T� J� =� -40°C� to� +85°C,� Unless� Otherwise� Specified.� Parameters� with� MIN� and/or� MAX�

�limits� are� 100%� tested� at� +25°C,� unless� otherwise� specified.� Temperature� limits� established� by� characterization�

�and� are� not� production� tested.� (Continued)�

�PARAMETER�

�SYSRST� Low� Output� Voltage�

�SYSRST� Output� Capacitance�

�SYSRST� Low� to� GATE� Turn-off�

�SYSRST� High� to� GATE� Turn-on�

�SYMBOL�

�V� OL_SRST�

�C� OUT_SRST�

�t� delSYS_G_1�

�t� delSYS_G_2�

�TEST� CONDITIONS�

�V� DD� =� 5V,� I� OUT� =� 100� μ� A�

�GATE� =� 80%� of� V� DD� +5V�

�GATE� =� 50%� of� V� DD� +5V�

�MIN�

�-�

�-�

�-�

�-�

�TYP�

�10�

�40�

�0.4�

�MAX�

�0.1�

�-�

�-�

�-�

�UNIT�

�V�

�pF�

�ns�

�ms�

�GATE�

�GATE� Turn-On� Current�

�GATE� Turn-Off� Current�

�GATE� Current� Range�

�GATE� Pull-Down� High� Current�

�I� GATEon�

�I� GATEoff_l�

�I� GATE_range�

�I� GATEoff_h�

�GATE� =� 0V�

�GATE� =� V� DD� ,� Disabled�

�Within� IC� I� GATE� max-min�

�GATE� =� V� DD� ,� UVLO� =� 0V�

�8.3�

�-12.5�

�-�

�-�

�10.2�

�-10.2�

�0.6�

�75�

�12.5�

�-8.3�

�3�

�-�

�μA�

�μA�

�μA�

�mA�

�GATE� High� Voltage�

�V� GATEh5�

�V� DD� =� 5V�

�V� DD� +� 5.3V� V� DD� +� 5.6V�

�-�

�V�

�GATE� Low� Voltage�

�V� GATEl�

�Gate� Low� Voltage,� V� DD� =� 1V�

�-�

�0.01�

�0.1�

�V�

�BIAS�

�IC� Supply� Current�

�ISL8723� Stand� By� IC� Supply� Current�

�V� DD� Power� On� Reset�

�I� VDD_5V�

�I� VDD_sb�

�V� DD� _POR�

�V� DD� =� 5V,� Enabled� and� static�

�V� DD� =� 5V,� ENABLE� =� 0V�

�V� DD� rising�

�-�

�-�

�-�

�0.48�

�30�

�2.2�

�0.6�

�40�

�2.41�

�mA�

�μA�

�V�

�ISL8723,� ISL8724� Descriptions� and�

�Operation�

�The� ISL8723� and� ISL8724� sequencers� are� quad� voltage�

�sequencing� controllers� designed� for� use� in� multiple-voltage�

�systems� requiring� power� sequencing� of� various� supply�

�voltages.� Individual� voltage� rails� are� gated� on� and� off� by�

�external� N-Channel� MOSFETs,� the� gates� of� which� are�

�driven� by� an� internal� charge� pump� to� ~V� DD� +5.6V� (VQP)� in�

�a� user� programmed� sequence.�

�With� the� ISL8723,� the� ENABLE� must� be� asserted� high� and�

�all� four� voltages� to� be� sequenced� must� be� above� their�

�respective� user� programmed� Undervoltage� Lock� Out�

�(UVLO)� levels� before� programmed� output� turn� on�

�sequencing� can� begin.� Sequencing� and� delay�

�determination� is� accomplished� by� the� choice� of� external�

�capacito� r� values� on� the� DLY_ON� and� DLY_OFF� pins.� The�

�SYSRST� goes� high� once� all� 4� UVLO� inputs� and� ENABLE�

�are� satisfied.� Once� all� 4� UVLO� inputs� and� ENABLE� are�

�satisfied� for� 10ms,� the� four� DLY_ON� capacitors� are�

�simultaneously� charged� with� 1μA� current� sources� to� the�

�DLY_Vth� level� of� 1.28V.� As� each� DLY_ON� pin� reaches� the�

�DLY_Vth� level,� its� associated� GATE� will� then� turn-on� with� a�

�10μA� source� current� to� the� VQP� voltage� of� V� DD� +� 5.6V.�

�Thus,� all� four� GATEs� will� sequentially� turn� on.� Once� at�

�DLY_Vth� the� DLY_ON� pins� will� discharge� to� be� ready� when�

�next� needed.� After� the� entire� turn� on� sequence� has� been�

�completed� and� all� GATEs� have� reached� the� charge�

�pumped� voltage� (VQP),� a� 160ms� delay� is� started� to� ensure�

�stability� after� which� the� RESET� output� will� be� released� to� go�

�high.� Subsequent� to� turn-on,� if� any� input� falls� below� its�

�5�

�UVLO� point� for� longer� than� the� glitch� filter� period,� t� FIL�

�(~7μs)� this� is� considered� a� fault.� RESET,� SYSRST� and� all�

�GATEs� are� simultaneously� pulled� low.� In� this� mode� the�

�GATEs� are� pulled� low� with� ~75mA.� Normal� shutdown� mode�

�is� entered� when� no� UVLO� is� violated� and� the� ENABLE� is�

�deasserted.� When� ENABLE� is� deasserted,� RESET� is�

�asserted� and� pulled� low.� Next,� all� four� shutdown� ramp�

�capacitors� on� the� DLY_OFF� pins� are� charged� with� a� 1μA�

�source� and� when� any� ramp-capacitor� reaches� DLY_Vth,� a�

�latch� is� set� and� a� 10μA� current� is� sunk� on� the� respective�

�GATE� pin� to� turn� off� its� external� MOSFET.� When� the� falling�

�GATE� voltage� is� approximately� 1.5V,� the� GATE� is� pulled�

�down� the� rest� of� the� way� at� a� higher� current� level� to� ensure�

�a� hard� turn-off.� Each� individual� external� FET� is� thus� turned�

�off� removing� the� voltages� from� the� load� in� the� programmed�

�sequence.� The� SYSRST� will� pull� low� concurrent� with� the�

�last� GATE� being� pulled� low.�

�The� ISL8723� and� ISL8724� have� the� same� functionality�

�except� for� the� complimentary� ENABLE� active� polarity� with�

�the� ISL8724� having� an� ENABLE� input.� Additionally,� the�

�ISL8723� also� has� a� low� power� sleep� state� when� disabled.�

�Upon� bias,� the� SYSRST� and� RESET� pins� are� held� low�

�before� bias� voltage� =� 1V.�

�The� SYSRST� has� both� an� input� and� output� function.� As� an�

�output,� the� SYSRST� pin� is� useful� when� implementing�

�multiple� sequencers� in� a� design� needing� simultaneous�

�shutdown� as� with� a� kill� switch� across� all� sequencers.� Once�

�any� UVLO� is� unsatisfied� for� longer� than� t� FIL� ,� the� related�

�SYSRST� will� pull� low� and� pull� all� other� SYSRST� pins� low�

�FN6413.1�

�April� 22,� 2009�

�相关PDF资料 |

PDF描述 |

|---|---|

| T95Z336K016CZAL | CAP TANT 33UF 16V 10% 2910 |

| TC1303A-ZS0EUN | IC REG DL BCK/LINEAR SYNC 10MSOP |

| C1005X7R1E152M | CAP CER 1500PF 25V 20% X7R 0402 |

| M7PXK-1506J | D-SUB CABLE - MMM15K/MC16G/X |

| EMC49DRTS-S13 | CONN EDGECARD 98POS .100 EXTEND |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL8723IRZ | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL8723IRZR5369 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Intersil Corporation 功能描述: |

| ISL8723IRZ-T | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

| ISL8723IRZ-TR5369 | 制造商:Intersil Corporation 功能描述: |

| ISL8724IRZ | 功能描述:IC POWER SUPPLY SEQUENCER 24QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 电源控制器,监视器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 应用:多相控制器 输入电压:- 电源电压:9 V ~ 14 V 电流 - 电源:- 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:40-WFQFN 裸露焊盘 供应商设备封装:40-TQFN-EP(5x5) 包装:带卷 (TR) |

发布紧急采购,3分钟左右您将得到回复。