参数资料

| 型号: | ISL9444IRZ |

| 厂商: | Intersil |

| 文件页数: | 3/24页 |

| 文件大小: | 0K |

| 描述: | IC REG CTRLR BUCK PWM CM 40-QFN |

| 标准包装: | 60 |

| PWM 型: | 电流模式 |

| 输出数: | 3 |

| 频率 - 最大: | 1.32MHz |

| 电源电压: | 4.5 V ~ 28 V |

| 降压: | 是 |

| 升压: | 无 |

| 回扫: | 无 |

| 反相: | 无 |

| 倍增器: | 无 |

| 除法器: | 无 |

| Cuk: | 无 |

| 隔离: | 无 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 40-VFQFN 裸露焊盘 |

| 包装: | 管件 |

�� �

�

�

�ISL9444�

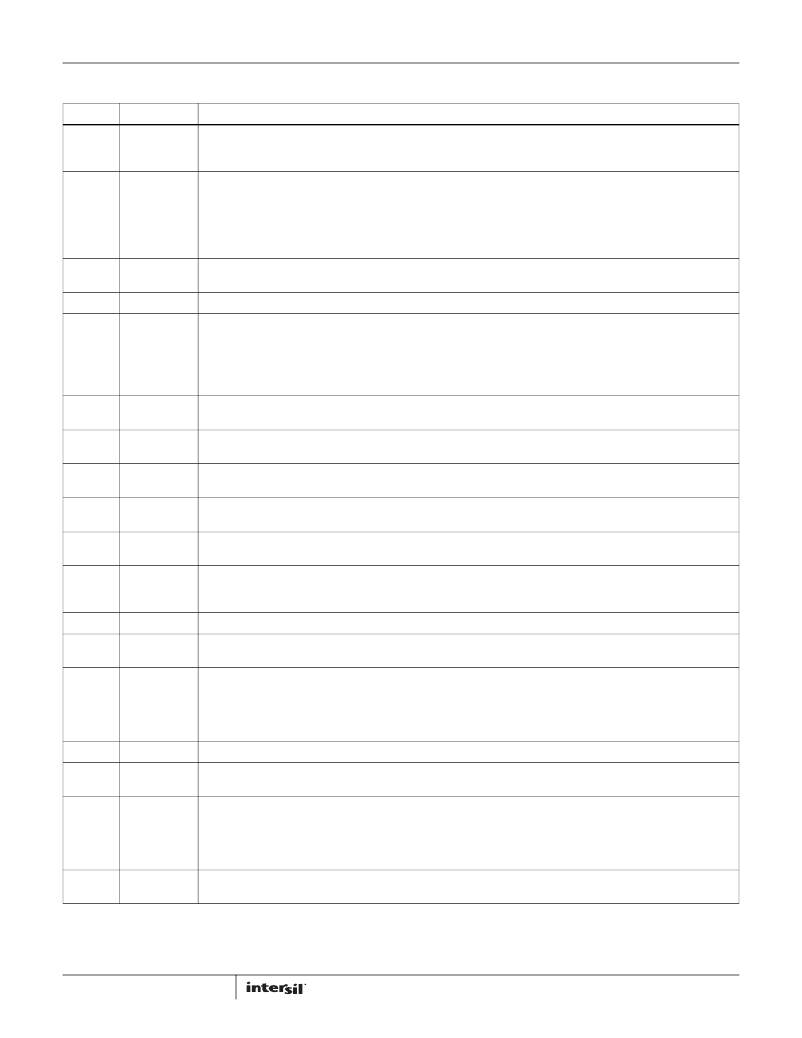

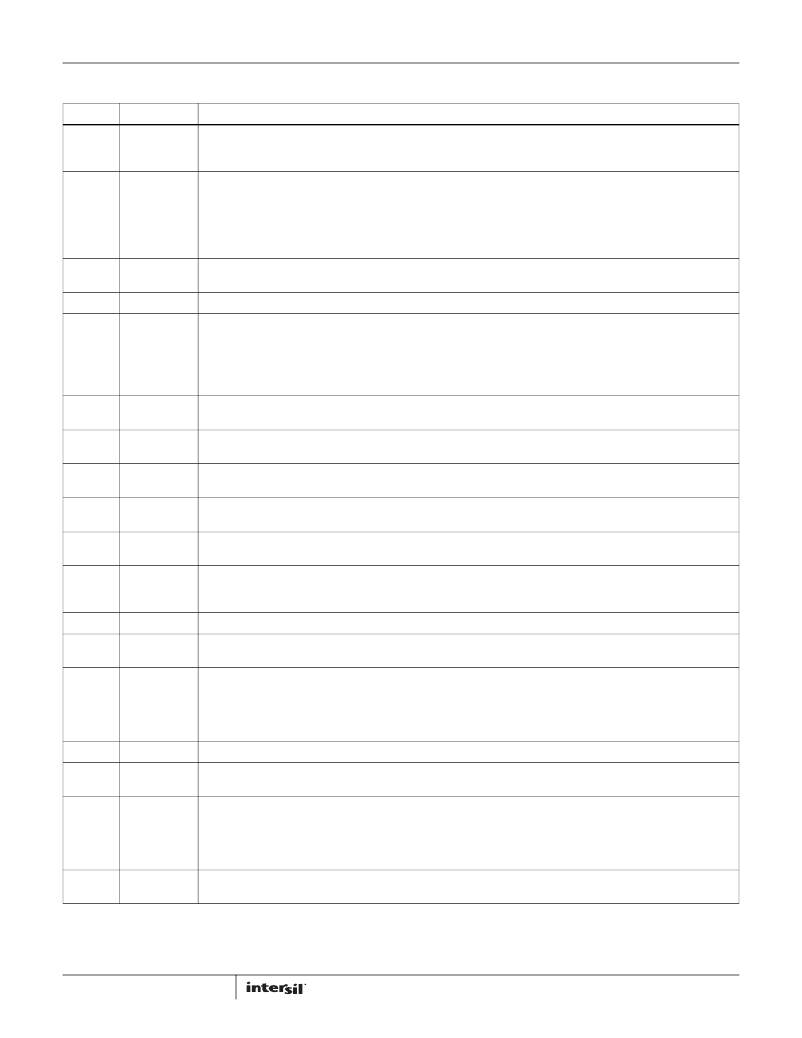

�Pin� Descriptions� (Continued)�

�PIN�

�5�

�6�

�7�

�8�

�9�

�10�

�11�

�12�

�13�

�14�

�15�

�16�

�17�

�18�

�19�

�20�

�21�

�22�

�NAME�

�VIN�

�EN/SS1�

�FB1�

�OCSET1�

�RT�

�PGOOD1�

�PGOOD2�

�PGOOD3�

�PG3_DLY�

�EN2�

�SGND�

�OCSET2�

�FB2�

�TK/SS2�

�OCSET3�

�FB3�

�TK/SS3�

�EN3�

�FUNCTION�

�This� pin� should� be� tied� to� the� input� rail.� It� provides� power� to� the� internal� linear� drive� circuitry� and� is� also� used� by� the�

�feed-forward� controller� to� adjust� the� amplitude� of� each� PWM� sawtooth.� Decouple� this� pin� with� a� small� ceramic� capacitor�

�(0.1μF� to� 1μF)� to� ground.�

�This� pin� provides� an� enable/disable� function� and� soft-starting� for� PWM1� output.� The� output� is� disabled� when� the� pin� is�

�pulled� to� GND.� During� start-up,� a� regulated� 1.55μA� soft-start� current� charges� an� external� capacitor� connected� at� this� pin.�

�When� the� voltage� on� the� EN/SS1� pin� reaches� 1.3V,� the� PWM1� output� becomes� active.� From� 1.3V� to� 2.0V,� the� reference�

�voltage� of� the� PWM1� is� clamped� to� the� voltage� at� EN/SS1� minus� 1.3V.� The� capacitance� of� the� soft-start� capacitors� sets�

�the� soft-starting� time� and� enable� delay� time.� Setting� the� soft-starting� time� too� short� might� create� undesirable� overshoot�

�at� the� output� during� start-up.� VCC_5V� UVLO� discharges� the� EN/SS1� via� an� internal� MOSFET.�

�PWM1� feedback� input.� Connect� FB1� to� a� resistive� voltage� divider� from� the� output� of� PWM1� to� GND� to� adjust� the� output�

�voltage.�

�A� resistor� from� this� pin� to� ground� adjusts� the� overcurrent� threshold� for� PWM1.�

�A� resistor� from� this� pin� to� ground� adjusts� the� switching� frequency� from� 200kHz� to� 1.2MHz.� The� switching� frequency� of�

�the� PWM� controller� is� determined� by� the� resistor,� R� T� ,�

�R� T� =� (� 23.36� ×� (� 1.5� ×� t� SW� –� 0.36� )� )� ?� k� Ω�

�(EQ.� 1)�

�where� t� SW� is� the� switching� period� in� μs.�

�Open� drain� logic� output� used� to� indicate� the� status� of� the� PWM1� output� voltage.� This� pin� is� pulled� down� when� the� PWM1�

�output� is� not� within� ±11%� of� the� nominal� voltage.�

�Open� drain� logic� output� used� to� indicate� the� status� of� the� PWM2� output� voltage.� This� pin� is� pulled� down� when� the� PWM2�

�output� is� not� within� ±11%� of� the� nominal� voltage.�

�Open� drain� logic� output� used� to� indicate� the� status� of� the� PWM3� output� voltage.� This� pin� is� pulled� down� when� the� PWM3�

�output� is� not� within� ±11%� of� the� nominal� voltage.�

�A� capacitor� connected� between� this� pin� and� ground� sets� a� delay� between� PWM3� output� voltage� reaching� ±11%� of�

�regulation� and� PGOOD3� going� high.� There� is� no� delay� when� PWM3� goes� out� of� regulation� and� PGOOD3� is� pulled� low.�

�Enable/Disable� input� for� PWM2.� The� output� of� PWM2� is� enabled� when� this� pin� is� pulled� HIGH,� and� disabled� when� this� pin�

�is� pulled� LOW.� PGOOD2� is� pulled� LOW� 1μs� after� EN2� is� pulled� LOW.� Do� not� leave� this� pin� floating.�

�This� is� the� small-signal� ground� common� to� all� 3� controllers.� It� is� suggested� to� route� this� separately� from� the� high� current�

�ground� (PGND).� SGND� and� PGND� can� be� tied� together� if� there� is� one� solid� ground� plane� with� no� noisy� currents� around� the�

�chip.� All� voltage� levels� are� measured� with� respect� to� this� pin.�

�A� resistor� from� this� pin� to� ground� adjusts� the� overcurrent� threshold� for� PWM2.�

�PWM2� feedback� input.� Connect� FB2� to� a� resistive� voltage� divider� from� the� output� of� PWM2� to� GND� to� adjust� the� output�

�voltage.�

�Dual� function� pin.� The� reference� voltage� of� PWM2� is� clamped� to� the� voltage� at� TK/SS2� during� start-up.� When� this� pin� is�

�used� for� tracking,� another� channel� is� configured� as� the� master� and� the� output� voltage� of� the� master� channel� is� applied�

�to� this� pin� via� a� resistor� divider.�

�When� used� for� soft-starting� control,� a� soft-start� capacitor� is� connected� from� this� pin� to� GND.� A� regulated� 1.55μA� soft-starting�

�current� charges� up� the� soft-start� capacitor.� Value� of� the� soft-start� capacitor� sets� the� PWM2� output� voltage� ramp.�

�A� resistor� from� this� pin� to� ground� adjusts� the� overcurrent� threshold� for� PWM3.�

�PWM3� feedback� input.� Connect� FB3� to� a� resistive� voltage� divider� from� the� output� of� PWM3� to� GND� to� adjust� the� output�

�voltage.�

�Dual� function� pin.� The� reference� voltage� of� PWM3� is� clamped� to� the� voltage� at� TK/SS3� during� start-up.� When� this� pin� is�

�used� for� tracking,� another� channel� is� configured� as� the� master� and� the� output� voltage� of� the� master� channel� is� applied�

�to� this� pin� via� a� resistor� divider.�

�When� used� for� soft-starting� control,� a� soft-start� capacitor� is� connected� from� this� pin� to� GND.� A� regulated� 1.55μA� soft-starting�

�current� charges� up� the� soft-start� capacitor.� Value� of� the� soft-start� capacitor� sets� the� PWM3� output� voltage� ramp.�

�Enable/Disable� input� for� PWM3.� The� output� of� PWM3� is� enabled� when� this� pin� is� pulled� HIGH,� and� disabled� when� this� pin�

�is� pulled� LOW.� PGOOD3� is� pulled� LOW� 1μs� after� EN3� is� pulled� LOW.� Do� not� leave� this� pin� floating.�

�3�

�FN7665.3�

�May� 29,� 2012�

�相关PDF资料 |

PDF描述 |

|---|---|

| ISL9491ERZ | IC REG SGL LNB CONTROL 16QFN |

| ISL9492ERZ-T | IC REG SGL LNB CONTROL 28TQFN |

| ISL9506HRZ | IC REG CTRLR BUCK PWM 40-QFN |

| ISL95210IRZ | IC REG BUCK SYNC ADJ 10A 32QFN |

| ISL95870BIRZ | IC CTRLR PWM 1PHASE GPU 20QFN |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL9444IRZS2750 | 制造商:Intersil Corporation 功能描述:PB FREE. ISL9444 TRIPLE, STEP- DOWN PWM CONTROLLER IMVP-6. 4 - Rail/Tube |

| ISL9444IRZ-T | 功能描述:IC REG CTRLR BUCK PWM CM 40-QFN RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 切换控制器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- PWM 型:电流模式 输出数:1 频率 - 最大:275kHz 占空比:50% 电源电压:18 V ~ 110 V 降压:无 升压:无 回扫:无 反相:无 倍增器:无 除法器:无 Cuk:无 隔离:是 工作温度:-40°C ~ 85°C 封装/外壳:8-SOIC(0.154",3.90mm 宽) 包装:带卷 (TR) |

| ISL9444IRZ-T7A | 功能描述:软开关 PWM 控制器 ISL9444 TRIPLE STEP DWN PWM CONTRLR RoHS:否 制造商:Fairchild Semiconductor 输出端数量: 输出电流: 开关频率: 工作电源电压:30 V 电源电流: 最大工作温度:+ 105 C 最小工作温度:- 40 C 安装风格:SMD/SMT 封装 / 箱体:SOIC-8 封装:Reel |

| ISL9444IRZ-T7AS2750 | 制造商:Intersil Corporation 功能描述:ISL9444 TRIPLE, STEP- DOWN PWM CONTROLLER IMVP-6. 40 LD MLFP - Tape and Reel |

| ISL9444IRZ-TS2750 | 制造商:Intersil Corporation 功能描述:PB FREE. ISL9444 TRIPLE, STEP- DOWN PWM CONTROLLER IMVP-6. 4 - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。