- 您现在的位置:买卖IC网 > PDF目录16320 > ISL98003CNZ-EVALZ (Intersil)EVAL BOARD FOR ISL98003CNZ PDF资料下载

参数资料

| 型号: | ISL98003CNZ-EVALZ |

| 厂商: | Intersil |

| 文件页数: | 15/31页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR ISL98003CNZ |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页当前第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

22

FN6760.0

September 12, 2008

The offset controls shift the entire RGB input range, changing

the input image brightness. Three separate registers provide

independent control of the R, G, and B channels. Their

nominal setting is 0x8000, which forces the ADC to output

code 0x00 (or 0x80 for the R (Pr) and B (Pb) channels in

YPbPr mode) during the back porch period when ABLC is

enabled.

Functional Description

Inputs

The ISL98003 digitizes analog video inputs in both RGB

and Component (YPbPr) formats, with or without

embedded sync (SOG).

RGB Inputs

For RGB inputs, the black/blank levels are identical and equal

to 0V. The range for each color is typically 0V to 0.7V from

black to white. HSYNC and VSYNC are separate signals.

Component YPbPr Inputs

In addition to RGB and RGB with SOG, the ISL98003 has an

option that is compatible with the component YPbPr video

inputs typically generated by DVD players. While the

ISL98003 digitizes signals in these color spaces, it does not

perform color space conversion; if it digitizes an RGB signal,

it outputs digital RGB, while if it digitizes a YPbPr signal, it

outputs digital YCbCr, also called YUV.

The Luminance (Y) signal is applied to the Green Channel

and is processed in a manner identical to the Green input

with SOG described previously. The color difference signals

Pb and Pr are bipolar and swing both above and below the

black level. When the YPbPr mode is enabled, the black

level output for the color difference channels shifts to a mid

scale value of 0x80. Setting configuration register

0x10[4] = 1 enables the YPbPr signal processing mode of

operation.

The ISL98003 can optionally decimate the incoming data to

provide a 4:2:2 output stream (configuration register

0x28[0] = 1) as shown in Table 2.

Input Coupling

Inputs can be either AC-coupled (default) or DC-coupled

(see register 0x10[3]). AC coupling is usually preferred since

it allows video signals with substantial DC offsets to be

accurately digitized. The ISL98003 provides a complete

internal DC-restore function, including the DC-restore clamp

(see Figure 1) and programmable clamp timing (registers

0x24, 0x25, and 0x26).

When AC-coupled, the DC-restore clamp is applied every

line, a programmable number of pixels after the trailing edge

of HSYNC. If register 0x60[2] = 0 (the default), the clamp will

not be applied while the DPLL is coasting, preventing any

clamp voltage errors from composite sync edges,

equalization pulses, or Macrovision signals.

After the trailing edge of HSYNC, the DC-restore clamp is

turned on after the number of pixels specified in the

DC-Restore and ABLC Starting Pixel registers (0x24 and

0x25) has been reached. The clamp is applied for the

number of pixels specified by the DC-Restore Clamp Width

Register (0x26). The clamp can be applied to the back porch

of the video, or to the front porch (by increasing the

DC-Restore and ABLC Starting Pixel registers so all the

active video pixels are skipped).

Note: The Tri-level detect for Sync on Green (SOG) utilizes

the digitized data from the selected Green video channel. If

Tri-level Sync is present, the default DC Clamp start position

will clamp at the top of the Tri-level Sync pulse giving a false

negative for Tri-level detect and clamping off the bottom half

of the green video. If you have an indication of active SOG

you must move the clamp start to a value greater than 0x30

to check to see if the Tri-level Sync is present.

If DC-coupled operation is desired, the input to the ADC will

be the difference between the input signal (RIN1, for

example) and ground.

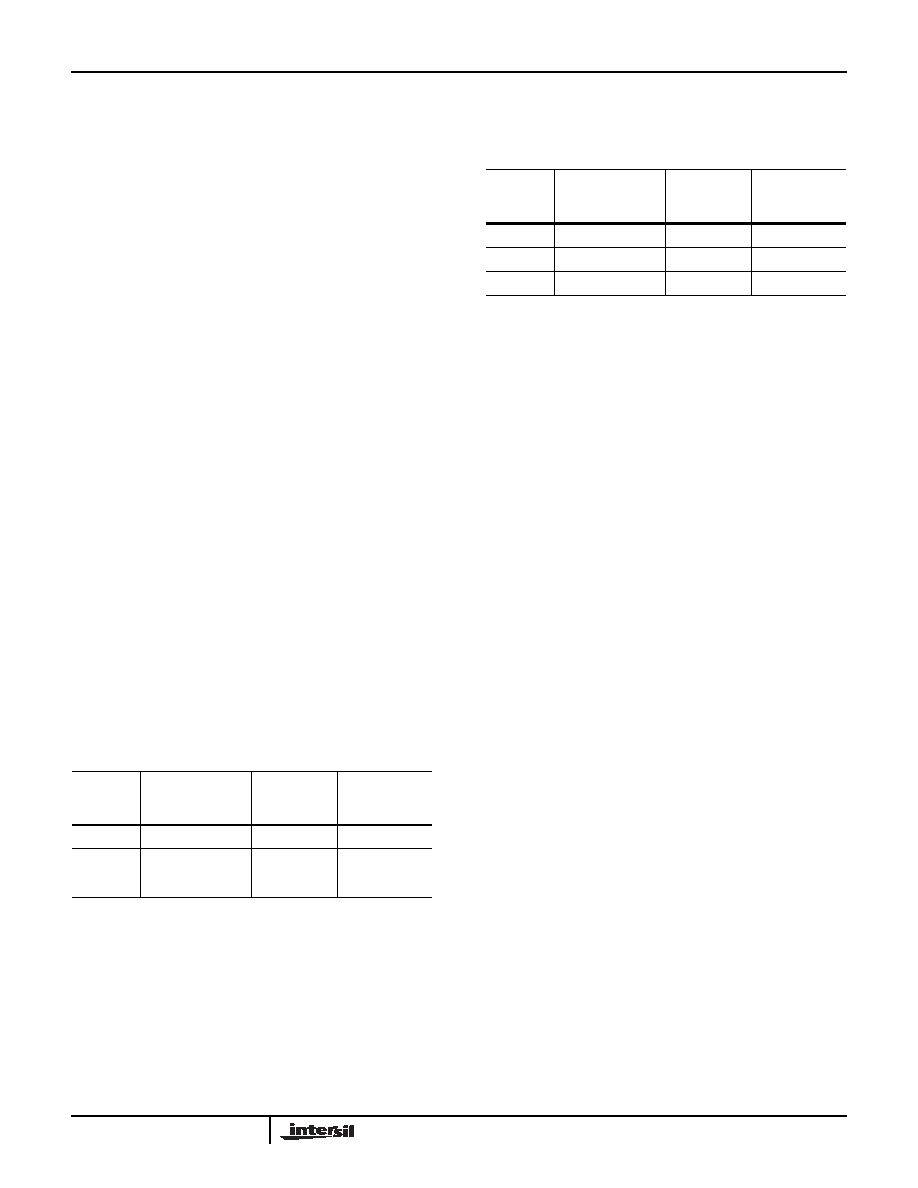

TABLE 1. YUV MAPPING (4:4:4)

INPUT

SIGNAL

ISL98003

INPUT

CHANNEL

ISL98003

OUTPUT

ASSIGNMENT

OUTPUT

SIGNAL

Y

Green

Y0Y1Y2Y3

Pb

Blue

U0U1U2U3

Pr

Red

V0V1V2V3

TABLE 2. YUV MAPPING (4:2:2)

INPUT

SIGNAL

ISL98003

INPUT

CHANNEL

ISL98003

OUTPUT

ASSIGNMENT

OUTPUT

SIGNAL

Y

Green

Y0Y1Y2Y3

Pb

Blue

Driven Low

Pr

Red

U0V0U2V2

ISL98003

相关PDF资料 |

PDF描述 |

|---|---|

| VE-J1T-EZ-F3 | CONVERTER MINIMOD DC/DC 6.5V 25W |

| 3-1906013-3 | CA 2.0MM OFNR 50/125,LC SEC BLU |

| A1RXB-2636G | IDC CABLE - APR26B/AE26G/X |

| EET-ED2W151BA | CAP ALUM 150UF 450V 20% SNAP |

| A3BRB-2018G | IDC CABLE - ASR20B/AE20G/APR20B |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL98003INZ-110 | 功能描述:IC AFE 3CH 8BIT 110MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003INZ-EVALZ | 功能描述:EVALUATION BOARD FOR ISL98003INZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ISL98012IUZ | 功能描述:直流/直流开关转换器 1.8V INPUT PWM STP UPG 10LD RoHS:否 制造商:STMicroelectronics 最大输入电压:4.5 V 开关频率:1.5 MHz 输出电压:4.6 V 输出电流:250 mA 输出端数量:2 最大工作温度:+ 85 C 安装风格:SMD/SMT |

| ISL98012IUZ-T | 功能描述:IC REG BOOST ADJ 0.6A 10MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:降压(降压) 输出类型:两者兼有 输出数:1 输出电压:5V,1 V ~ 10 V 输入电压:3.5 V ~ 28 V PWM 型:电流模式 频率 - 开关:220kHz ~ 1MHz 电流 - 输出:600mA 同步整流器:无 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:16-SSOP(0.154",3.90mm 宽) 包装:带卷 (TR) 供应商设备封装:16-QSOP |

| ISL98012IUZ-TK | 功能描述:IC REG BOOST ADJ 0.6A 10MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 标准包装:1 系列:EZBuck™ 类型:降压(降压) 输出类型:可调式 输出数:1 输出电压:0.8 V ~ 22.1 V 输入电压:3 V ~ 26 V PWM 型:电流模式 频率 - 开关:1.5MHz 电流 - 输出:1.8A 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WFDFN 裸露焊盘 包装:剪切带 (CT) 供应商设备封装:8-DFN(2x2) 其它名称:785-1276-1 |

发布紧急采购,3分钟左右您将得到回复。