- 您现在的位置:买卖IC网 > PDF目录16320 > ISL98003CNZ-EVALZ (Intersil)EVAL BOARD FOR ISL98003CNZ PDF资料下载

参数资料

| 型号: | ISL98003CNZ-EVALZ |

| 厂商: | Intersil |

| 文件页数: | 17/31页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR ISL98003CNZ |

| 标准包装: | 1 |

| 系列: | * |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页当前第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页

24

FN6760.0

September 12, 2008

Intersil’s DPLL has the capability to correct large phase

changes almost instantly by maximizing the phase error gain

while keeping the frequency gain relatively low. This is done

by changing the contents of register 0x74 to 0x4C. This

increases the phase error gain to 100%. Because a phase

setting, this high will slightly increase jitter, the default setting

(0x49) for register 0x74 is recommended for all other sync

sources.

Sync Timing Measurement

The ISL98003 analyzes the timing characteristics of the sync

signals for the currently selected input channel and presents

the results in registers 0x40 through 0x46.

The HSYNC period and pulse width values are 16-bit

numbers representing the number of crystal clocks in 16

consecutive periods or pulse widths giving a measurement

resolution of 1/16th of a crystal clock.

The VSYNC period is a 12-bit number representing the

number of either HSYNCs or units of 512 crystal clocks that

occur in one video frame. The default is to count HSYNC

pulses, but setting register 0x4F[0] = 1 changes to the units

to crystal clock/512.

The VSYNC pulse width is a 12-bit number representing the

number of either HSYNCs or units of 512 crystal clocks that

occur in one VSYNC. The default is to count HSYNC pulses,

but setting register 0x4F[0] = 1 changes to the units to

crystal clock/512.

PGA

The ISL98003’s Programmable Gain Amplifier (PGA) has a

nominal gain range from 0.5V/V (-6dB) to 2.0V/V (+6dB).

The transfer function is shown in Equation 1:

where GainCode is the value in the Gain register for that

particular color. Note that for a gain of 1V/V, the GainCode

should be 85 (0x55). This is a different center value than the

128 (0x80) value used by some other AFEs, so the firmware

should take this into account when adjusting gains.

The PGAs are updated by the internal clamp signal once per

line. In normal operation this means that there is a maximum

delay of one HSYNC period between a write to a Gain

register for a particular color and the corresponding change

in that channel’s actual PGA gain. If there is no regular

HSYNC/SOG source, or if the external clamp option is

enabled (register 0x10[7:6]) but there is no external clamp

signal being generated, it may take up to 100ms for a write

to the Gain register to update the PGA. This is not an issue

in normal operation with RGB and YPbPr signals.

Offset DAC

The ISL98003 features a 10-bit Digital-to-Analog Converter

(DAC) to provide extremely fine control over the full channel

offset. The DAC is placed after the PGA to eliminate

interaction between the PGA (controlling “contrast”) and the

Offset DAC (controlling “brightness”).

In normal operation, the Offset DAC is controlled by the

ABLC circuit, ensuring that the offset is always reduced to

sub-LSB levels (see “Automatic Black Level Compensation

(ABLC)” on page 25 for more information). When ABLC is

enabled, the Offset register pairs (0x18 - 0x19, 0x1A -0x1B

and 0x1C - 0x1D) control a digital offset added to or

subtracted from the output of the ADC. This mode provides

the best image quality and eliminates the need for any

offset calibration.

If desired, ABLC can be disabled (0x27[0] = 1) and the

Offset DAC programmed manually, with the 8 most

significant bits in registers 0x18, 0x1A,10x1C, and the 2

least significant bits in registers 0x19[7:6], 0x1B[7:6] and

0x1D[7:6].

-

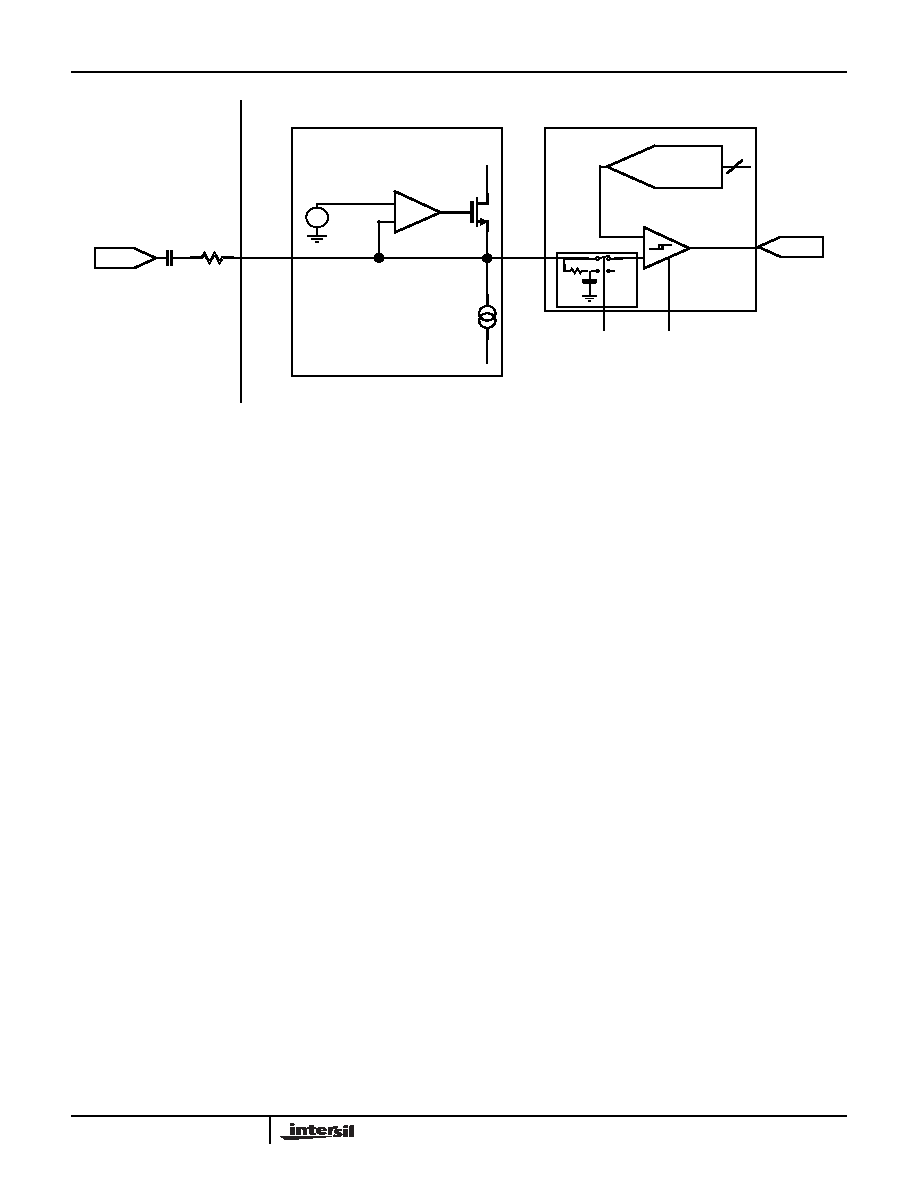

+

GREEN

SLICER DAC

600mV TO 900mV

+

–

600m V

SOGIN

1A

4

RIN

CIN

10nF

500

CLAM P

SLICE

FILTER

ON/OFF

HIST

ON/OFF

-

+

SYNCOUT

FIGURE 2. SOG SLICER

Ω

Gain

V

----

0.5

GainCode

170

-----------------------------

+

=

(EQ. 1)

ISL98003

相关PDF资料 |

PDF描述 |

|---|---|

| VE-J1T-EZ-F3 | CONVERTER MINIMOD DC/DC 6.5V 25W |

| 3-1906013-3 | CA 2.0MM OFNR 50/125,LC SEC BLU |

| A1RXB-2636G | IDC CABLE - APR26B/AE26G/X |

| EET-ED2W151BA | CAP ALUM 150UF 450V 20% SNAP |

| A3BRB-2018G | IDC CABLE - ASR20B/AE20G/APR20B |

相关代理商/技术参数 |

参数描述 |

|---|---|

| ISL98003INZ-110 | 功能描述:IC AFE 3CH 8BIT 110MHZ 80EPTQFP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 模拟前端 (AFE) 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 位数:- 通道数:2 功率(瓦特):- 电压 - 电源,模拟:3 V ~ 3.6 V 电压 - 电源,数字:3 V ~ 3.6 V 封装/外壳:32-VFQFN 裸露焊盘 供应商设备封装:32-QFN(5x5) 包装:带卷 (TR) |

| ISL98003INZ-EVALZ | 功能描述:EVALUATION BOARD FOR ISL98003INZ RoHS:是 类别:编程器,开发系统 >> 评估演示板和套件 系列:- 标准包装:1 系列:PCI Express® (PCIe) 主要目的:接口,收发器,PCI Express 嵌入式:- 已用 IC / 零件:DS80PCI800 主要属性:- 次要属性:- 已供物品:板 |

| ISL98012IUZ | 功能描述:直流/直流开关转换器 1.8V INPUT PWM STP UPG 10LD RoHS:否 制造商:STMicroelectronics 最大输入电压:4.5 V 开关频率:1.5 MHz 输出电压:4.6 V 输出电流:250 mA 输出端数量:2 最大工作温度:+ 85 C 安装风格:SMD/SMT |

| ISL98012IUZ-T | 功能描述:IC REG BOOST ADJ 0.6A 10MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 产品培训模块:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 标准包装:2,500 系列:- 类型:降压(降压) 输出类型:两者兼有 输出数:1 输出电压:5V,1 V ~ 10 V 输入电压:3.5 V ~ 28 V PWM 型:电流模式 频率 - 开关:220kHz ~ 1MHz 电流 - 输出:600mA 同步整流器:无 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:16-SSOP(0.154",3.90mm 宽) 包装:带卷 (TR) 供应商设备封装:16-QSOP |

| ISL98012IUZ-TK | 功能描述:IC REG BOOST ADJ 0.6A 10MSOP RoHS:是 类别:集成电路 (IC) >> PMIC - 稳压器 - DC DC 开关稳压器 系列:- 标准包装:1 系列:EZBuck™ 类型:降压(降压) 输出类型:可调式 输出数:1 输出电压:0.8 V ~ 22.1 V 输入电压:3 V ~ 26 V PWM 型:电流模式 频率 - 开关:1.5MHz 电流 - 输出:1.8A 同步整流器:无 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WFDFN 裸露焊盘 包装:剪切带 (CT) 供应商设备封装:8-DFN(2x2) 其它名称:785-1276-1 |

发布紧急采购,3分钟左右您将得到回复。