- 您现在的位置:买卖IC网 > PDF目录79605 > IT80C51-12D (ATMEL CORP) 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | IT80C51-12D |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | 1 MM HEIGHT, QFP-44 |

| 文件页数: | 46/109页 |

| 文件大小: | 10824K |

| 代理商: | IT80C51-12D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页当前第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页

29

AT32UC3A

9.4

Exceptions and Interrupts

AVR32UC incorporates a powerful exception handling scheme. The different exception sources,

like Illegal Op-code and external interrupt requests, have different priority levels, ensuring a well-

defined behavior when multiple exceptions are received simultaneously. Additionally, pending

exceptions of a higher priority class may preempt handling of ongoing exceptions of a lower pri-

ority class.

When an event occurs, the execution of the instruction stream is halted, and execution control is

passed to an event handler at an address specified in Table 9-4 on page 32. Most of the han-

dlers are placed sequentially in the code space starting at the address specified by EVBA, with

four bytes between each handler. This gives ample space for a jump instruction to be placed

there, jumping to the event routine itself. A few critical handlers have larger spacing between

them, allowing the entire event routine to be placed directly at the address specified by the

EVBA-relative offset generated by hardware. All external interrupt sources have autovectored

interrupt service routine (ISR) addresses. This allows the interrupt controller to directly specify

the ISR address as an address relative to EVBA. The autovector offset has 14 address bits, giv-

ing an offset of maximum 16384 bytes. The target address of the event handler is calculated as

(EVBA | event_handler_offset), not (EVBA + event_handler_offset), so EVBA and exception

code segments must be set up appropriately. The same mechanisms are used to service all dif-

ferent types of events, including external interrupt requests, yielding a uniform event handling

scheme.

An interrupt controller does the priority handling of the external interrupts and provides the

autovector offset to the CPU.

9.4.1

System stack issues

Event handling in AVR32 UC uses the system stack pointed to by the system stack pointer,

SP_SYS, for pushing and popping R8-R12, LR, status register and return address. Since event

code may be timing-critical, SP_SYS should point to memory addresses in the IRAM section,

since the timing of accesses to this memory section is both fast and deterministic.

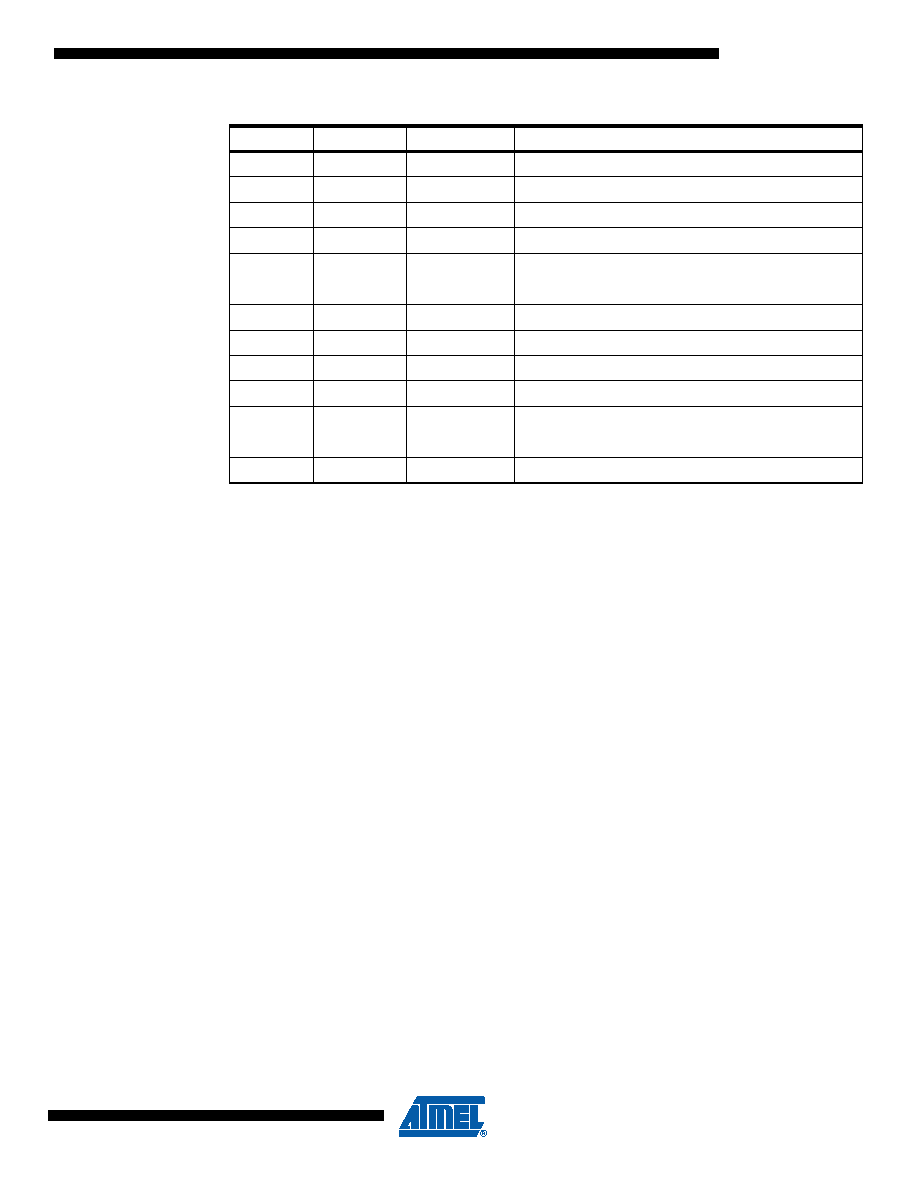

92

368

MPUPSR4

MPU Privilege Select Register region 4

93

372

MPUPSR5

MPU Privilege Select Register region 5

94

376

MPUPSR6

MPU Privilege Select Register region 6

95

380

MPUPSR7

MPU Privilege Select Register region 7

96

384

MPUCRA

Unused in this version of AVR32UC

97

388

MPUCRB

Unused in this version of AVR32UC

98

392

MPUBRA

Unused in this version of AVR32UC

99

396

MPUBRB

Unused in this version of AVR32UC

100

400

MPUAPRA

MPU Access Permission Register A

101

404

MPUAPRB

MPU Access Permission Register B

102

408

MPUCR

MPU Control Register

103-191

412-764

Reserved

Reserved for future use

192-255

768-1020

IMPL

IMPLEMENTATION DEFINED

Table 9-3.

System Registers (Continued)

Reg #

Address

Name

Function

32058K

AVR32-01/12

相关PDF资料 |

PDF描述 |

|---|---|

| IT80C31-25D | 8-BIT, 25 MHz, MICROCONTROLLER, PQFP44 |

| IF280C51C-36R | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

| IV80C32-L16R | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP44 |

| IQ80C52TXXX-L16D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, CQFP44 |

| IR80C52TXXX-20R | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CQCC44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| IT80C51-16 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| IT80C51-20 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| IT80C51-25 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| IT80C51-30 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| IT80C51-36 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。