参数资料

| 型号: | KAD5512P-12Q72 |

| 厂商: | Intersil |

| 文件页数: | 20/36页 |

| 文件大小: | 0K |

| 描述: | IC ADC 12BIT 125MSPS SGL 72-QFN |

| 产品培训模块: | High-Speed Analog-to-Digital Converters |

| 标准包装: | 1 |

| 系列: | FemtoCharge™ |

| 位数: | 12 |

| 采样率(每秒): | 125M |

| 数据接口: | 串行,SPI? |

| 转换器数目: | 1 |

| 功率耗散(最大): | 235mW |

| 电压电源: | 单电源 |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 72-VFQFN 裸露焊盘 |

| 供应商设备封装: | 72-QFN(10x10) |

| 包装: | 托盘 |

| 输入数目和类型: | 1 个差分,单极 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页当前第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页

KAD5512P

27

FN6807.4

October 1, 2010

ADDRESS 0X74: OUTPUT_MODE_B

ADDRESS 0X75: CONFIG_STATUS

Bit 6 DLL Range

This bit sets the DLL operating range to fast (default)

or slow.

Internal clock signals are generated by a delay-locked

loop (DLL), which has a finite operating range. Table 14

shows the allowable sample rate ranges for the slow and

fast settings.

.

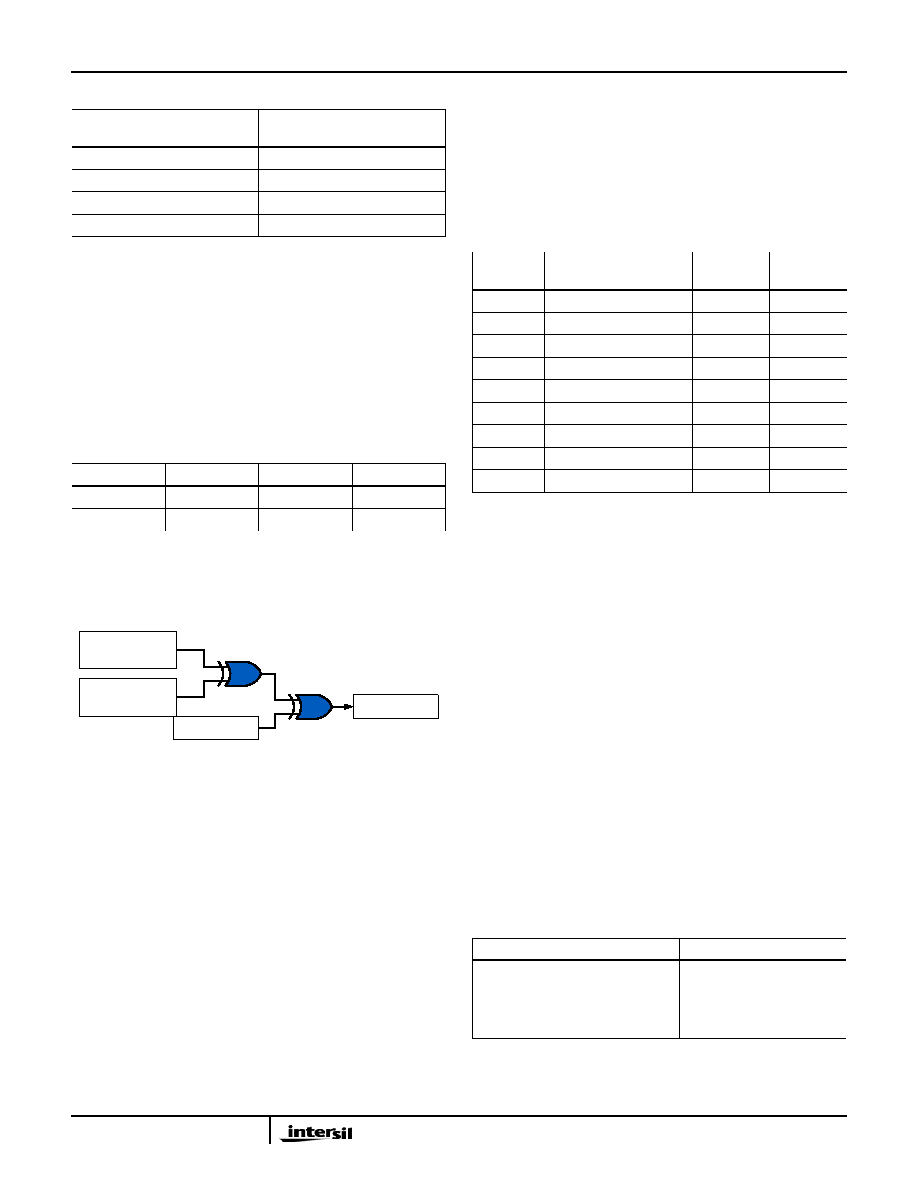

The output_mode_B and config_status registers are used

in conjunction to enable DDR mode and select the

frequency range of the DLL clock generator. The method

of setting these options is different from the other

registers.

The procedure for setting output_mode_B is shown in

Figure 42. Read the contents of output_mode_B and

config_status and XOR them. Then XOR this result with

the desired value for output_mode_B and write that XOR

result to the register.

Device Test

The KAD5512 can produce preset or user defined

patterns on the digital outputs to facilitate in-site testing.

A static word can be placed on the output bus, or two

different words can alternate. In the alternate mode, the

values defined as Word 1 and Word 2 (as shown in

Table 15) are set on the output bus on alternating clock

phases. The test mode is enabled asynchronously to the

sample clock, therefore several sample clock cycles may

elapse before the data is present on the output bus.

ADDRESS 0XC0: TEST_IO

Bits 7:6 User Test Mode

These bits set the test mode to static (0x00) or

alternate (0x01) mode. Other values are reserved.

The four LSBs in this register (Output Test Mode)

determine the test pattern in combination with registers

0xC2 through 0xC5. Refer to Table 17.

ADDRESS 0XC2: USER_PATT1_LSB AND

ADDRESS 0XC3: USER_PATT1_MSB

These registers define the lower and upper eight bits,

respectively, of the first user-defined test word.

ADDRESS 0XC4: USER_PATT2_LSB AND

ADDRESS 0XC5: USER_PATT2_MSB

These registers define the lower and upper eight bits,

respectively, of the second user-defined test word.

72 Pin/48 Pin Package Options

The KAD5512 is available in both 72 pin and 48 pin

packages. The 48 pin package option supports LVDS DDR

only. A reduced set of pin selectable functions are

available in the 48 pin package due to the reduced

pinout; (OUTMODE, OUTFMT, and CLKDIV pins are not

available). Table 16 shows the default state for these

functions for the 48 pin package. Note that these

functions are available through the SPI, allowing a user

to set these modes as they desire, offering the same

flexibility as the 72 pin package option. DC and AC

performance of the ADC is equivalent for both package

options.

TABLE 13. OUTPUT FORMAT CONTROL

VALUE

0x93[2:0]

OUTPUT FORMAT

000

Pin Control

001

Two’s Complement

010

Gray Code

100

Offset Binary

TABLE 14. DLL RANGES

DLL RANGE

MIN

MAX

UNIT

Slow

40

100

MSPS

Fast

80

fS MAX

MSPS

FIGURE 42. SETTING OUTPUT_MODE_B REGISTER

READ

CONFIG_STATUS

0x75

READ

OUTPUT_MODE_B

0x74

DESIRED

VALUE

WRITE TO

0x74

TABLE 15. OUTPUT TEST MODES

VALUE

0xC0[3:0]

OUTPUT TEST MODE

WORD 1

WORD 2

0000

Off

0001

Midscale

0x8000

N/A

0010

Positive Full-Scale

0xFFFF

N/A

0011

Negative Full-Scale

0x0000

N/A

0100

Checkerboard

0xAAAA

0x5555

0101

Reserved

N/A

0110

Reserved

N/A

0111

One/Zero

0xFFFF

0x0000

1000

User Pattern

user_patt1 user_patt2

TABLE 16. 48 PIN SPI - ADDRESSABLE FUNCTIONS

FUNCTION

DESCRIPTION

DEFAULT STATE

CLKDIV

Clock Divider

Divide by 1

OUTMODE

Output Driver

Mode

LVDS, 3mA (DDR)

OUTFMT

Data Coding

Two’s Complement

相关PDF资料 |

PDF描述 |

|---|---|

| MS27499E10F35SB | CONN RCPT 13POS BOX MNT W/SCKT |

| V24B24M250BL2 | CONVERTER MOD DC/DC 24V 250W |

| IDT82V2041EPP | IC LIU T1/J1/E1 1CH 44-TQFP |

| IDT82V2042EPFG8 | IC LIU T1/J1/E1 2CH SHORT 80TQFP |

| V24B24M250BL | CONVERTER MOD DC/DC 24V 250W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KAD5512P-17Q48 | 功能描述:模数转换器 - ADC 12-BIT 170MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-17Q72 | 功能描述:模数转换器 - ADC 12-BIT 170MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-21Q48 | 功能描述:模数转换器 - ADC 12-BIT 210MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-21Q72 | 功能描述:模数转换器 - ADC 12-BIT 210MSPS SINGL ADC PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

| KAD5512P-25Q48 | 功能描述:模数转换器 - ADC 12-BIT 250MSPS SINGL PROG LVDS/LVCMOS RoHS:否 制造商:Texas Instruments 通道数量:2 结构:Sigma-Delta 转换速率:125 SPs to 8 KSPs 分辨率:24 bit 输入类型:Differential 信噪比:107 dB 接口类型:SPI 工作电源电压:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:VQFN-32 |

发布紧急采购,3分钟左右您将得到回复。