- 您现在的位置:买卖IC网 > PDF目录16863 > KSZ8041NL-EVAL (Micrel Inc)BOARD EVALUATION FOR KSZ8041NL PDF资料下载

参数资料

| 型号: | KSZ8041NL-EVAL |

| 厂商: | Micrel Inc |

| 文件页数: | 6/54页 |

| 文件大小: | 0K |

| 描述: | BOARD EVALUATION FOR KSZ8041NL |

| 标准包装: | 1 |

| 主要目的: | 接口,以太网 PHY |

| 嵌入式: | 否 |

| 已用 IC / 零件: | KSZ8041NL |

| 主要属性: | 单芯片 PHY,10BASE-T/100BASE-TX |

| 次要属性: | MII,RMII,HP 自动 MDI,MDI-X 自动极性校正 |

| 已供物品: | 板 |

| 产品目录页面: | 1114 (CN2011-ZH PDF) |

| 相关产品: | 576-3296-5-ND - IC TXRX PHY 10/100 AUTO 32-MLF 576-2109-6-ND - IC TXRX PHY 10/100 LV/LP 32-MLF 576-2109-1-ND - IC TXRX PHY 10/100 LV/LP 32-MLF 576-2109-2-ND - IC TXRX PHY 10/100 LV/LP 32-MLF KSZ8041NLA3TR-ND - TRANSCEIVER 10/100 32-MLF 576-1645-6-ND - IC TXRX PHY 10/100 LV/LP 32-MLF 576-1645-1-ND - IC TXRX PHY 10/100 LV/LP 32-MLF 576-1645-2-ND - IC TXRX PHY 10/100 LV/LP 32-MLF |

| 其它名称: | 576-1621 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

Micrel, Inc.

KSZ8041NL/RNL

September 2010

14

M9999-090910-1.4

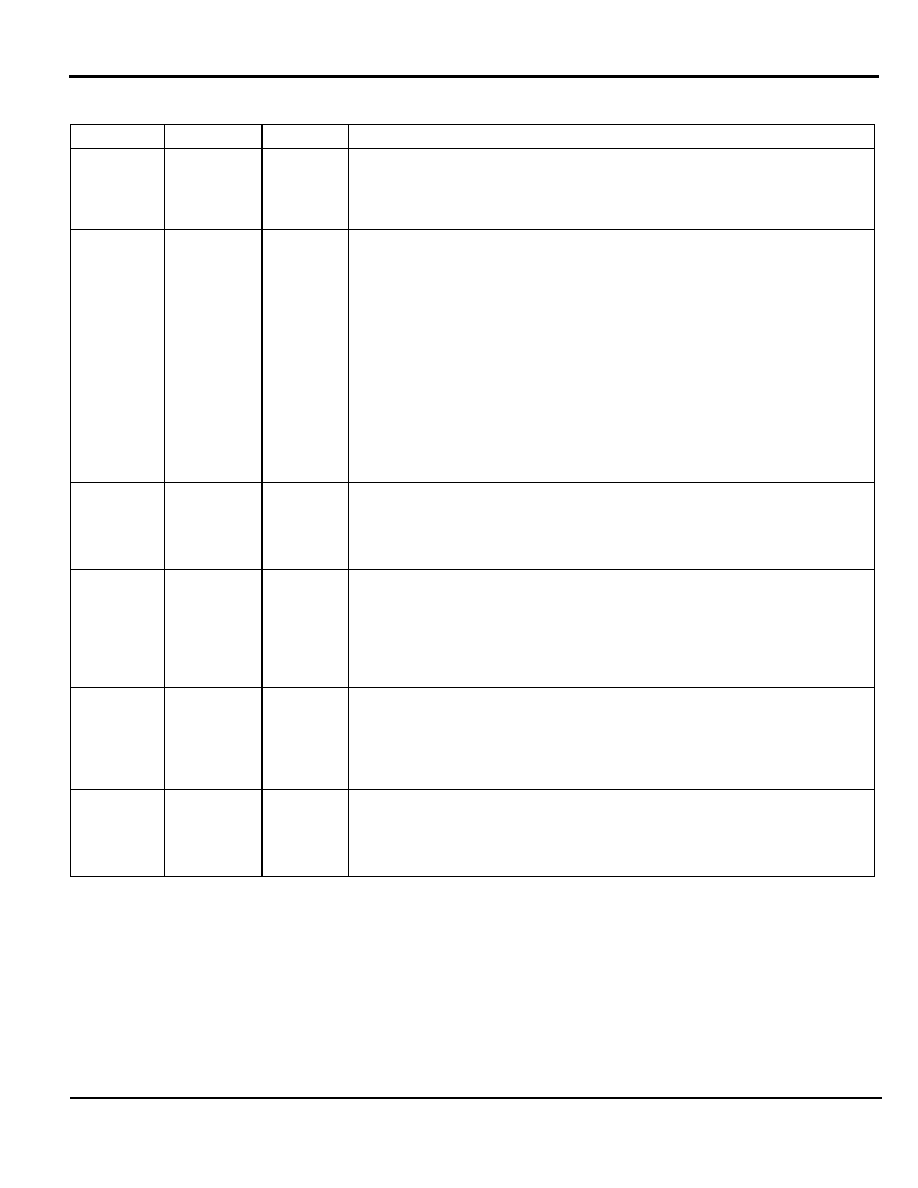

Strapping Options – KSZ8041NL

Pin Number

Pin Name

Type

(1)

Pin Function

15

14

13

PHYAD2

PHYAD1

PHYAD0

Ipd/O

Ipu/O

The PHY Address is latched at power-up / reset and is configurable to any value from

1 to 7.

The default PHY Address is 00001.

PHY Address bits [4:3] are always set to ‘00’.

18

29

28

CONFIG2

CONFIG1

CONFIG0

Ipd/O

The CONFIG[2:0] strap-in pins are latched at power-up / reset and are defined as

follows:

CONFIG[2:0]

Mode

000

MII (default)

001

RMII

010

Reserved – not used

011

Reserved – not used

100

MII 100Mbps Preamble Restore

101

Reserved – not used

110

Reserved – not used

111

Reserved – not used

20

ISO

Ipd/O

ISOLATE mode

Pull-up = Enable

Pull-down (default) = Disable

During power-up / reset, this pin value is latched into register 0h bit 10.

31

SPEED

Ipu/O

SPEED mode

Pull-up (default) = 100Mbps

Pull-down = 10Mbps

During power-up / reset, this pin value is latched into register 0h bit 13 as the Speed

Select, and also is latched into register 4h (Auto-Negotiation Advertisement) as the

Speed capability support.

16

DUPLEX

Ipu/O

DUPLEX mode

Pull-up (default) = Half Duplex

Pull-down = Full Duplex

During power-up / reset, this pin value is latched into register 0h bit 8 as the Duplex

Mode.

30

NWAYEN

Ipu/O

Nway Auto-Negotiation Enable

Pull-up (default) = Enable Auto-Negotiation

Pull-down = Disable Auto-Negotiation

During power-up / reset, this pin value is latched into register 0h bit 12.

Note:

1.

Ipu/O = Input with internal pull-up (40K +/-30%) during power-up/reset; output pin otherwise.

Ipd/O = Input with internal pull-down (40K +/-30%) during power-up/reset; output pin otherwise.

Pin strap-ins are latched during power-up or reset. In some systems, the MAC receive input pins may drive high during

power-up or reset, and consequently cause the PHY strap-in pins on the MII/RMII signals to be latched high. In this

case, it is recommended to add 1K pull-downs on these PHY strap-in pins to ensure the PHY does not strap-in to

ISOLATE mode, or is not configured with an incorrect PHY Address.

相关PDF资料 |

PDF描述 |

|---|---|

| DWP-125-1/2-0-STK | HEATSHRINK POLY 1/2"X4' BLK |

| SRR4028-270Y | INDUCTOR POWER 27UH 0.89A 4028 |

| RBC13DREH-S734 | CONN EDGECARD 26POS .100 EXTEND |

| H6MMH-2036G | DIP CABLE - HDM20H/AE20G/HDM20H |

| V110B24E150B | CONVERTER MOD DC/DC 24V 150W |

相关代理商/技术参数 |

参数描述 |

|---|---|

| KSZ8041NLI | 制造商:Micrel Inc 功能描述:IC TXRX PHY 10/100 LV/LP 32-MLF*NIC* |

| KSZ8041NLI TR | 功能描述:以太网 IC Physical Layer Transceiver 10/100BASE-T/TX (Lead Free) RoHS:否 制造商:Micrel 产品:Ethernet Switches 收发器数量:2 数据速率:10 Mb/s, 100 Mb/s 电源电压-最大:1.25 V, 3.45 V 电源电压-最小:1.15 V, 3.15 V 最大工作温度:+ 85 C 封装 / 箱体:QFN-64 封装:Tray |

| KSZ8041NLITR | 制造商:Micrel 功能描述:Physical Layer Transceiver 1Ch 100Mbps |

| KSZ8041NLI-TR | 功能描述:1/1 Transceiver Full MII, RMII 32-MLF? (5x5) 制造商:microchip technology 系列:- 包装:剪切带(CT) 零件状态:有效 类型:收发器 协议:MII,RMII 驱动器/接收器数:1/1 双工:全 接收器滞后:- 数据速率:- 电压 - 电源:3.135 V ~ 3.465 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:32-VFQFN 裸露焊盘,32-MLF? 供应商器件封装:32-MLF?(5x5) 标准包装:1 |

| KSZ8041NLJ | 制造商:MICREL 制造商全称:Micrel Semiconductor 功能描述:10/100 Ethernet Transceiver with Extended Temperature Support |

发布紧急采购,3分钟左右您将得到回复。