- 您现在的位置:买卖IC网 > PDF目录43903 > LC72134M PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 PDF资料下载

参数资料

| 型号: | LC72134M |

| 元件分类: | PLL合成/DDS/VCOs |

| 英文描述: | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 |

| 封装: | MFP-24 |

| 文件页数: | 24/27页 |

| 文件大小: | 463K |

| 代理商: | LC72134M |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页

No. 5814-6/27

LC72134M

Continued from preceding page.

Pin

Pin No.

Type

Function

Equivalent circuit

Main PLL

local oscillator

signal input

AMIN is selected when DVS in the serial data is set to 0.

When SNS in the serial data is set to 1:

Input frequency: 2 to 40 MHz

The signal is input to the swallow counter directly.

The divisor can be set to a value in the range 272 to 65535. The set value

becomes the actual divisor.

When SNS in the serial data is set to 0:

Input frequency: 0.5 to 10 MHz

The signal is input to a 12-bit programmable divider directly.

The divisor can be set to a value in the range 5 to 4095. The set value becomes

the actual divisor.

AMIN

17

Chip enable

This pin must be set high to enable serial data input (DI) or serial data output

(DO).

CE

2

Input data

Input for serial data transferred from the controller

DI

3

Clock

Clock used for data synchronization for serial data input (DI) and serial data

output (DO).

CL

4

Output data

Output for serial data transmitted to the controller. The content of the data

transmitted is determined by DOC0 through DOC2.

DO

5

Power supply

LC72134M power supply (VDD = 4.5 to 5.5 V)

The power on reset circuit operates when power is first applied.

——

VDD

19

Ground

LC72134M ground

——

VSS

23

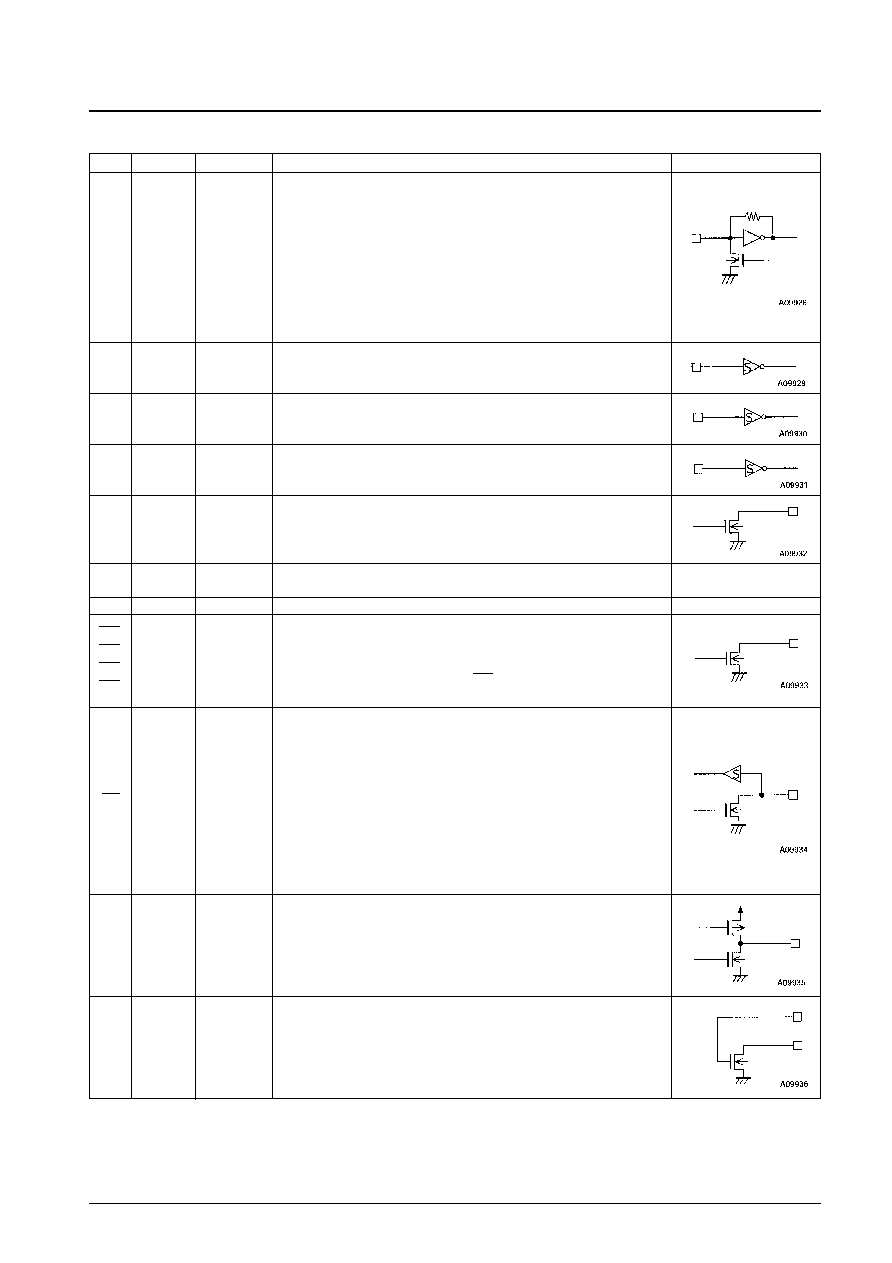

Output ports

Output-only ports

The output state is determined by BO1 through BO4 in the serial data.

When the data value is 0: The output state will be the open circuit state.

When the data value is 1: The output state will be a low level.

A time base signal (8 Hz) is output from BO1 when TBC in the serial data is set to

1.

BO1

BO2

BO3

BO4

6

7

8

14

I/O port

Shared function I/O port

The pin function is determined by IOC2 in the serial data.

When the data value = 0: Input port

When the data value = 1: Output port

When specified to function as an input port:

The input pin state is reported to the controller through the DO pin.

When the input state is low: The data will be 0:

When the input state is high: The data will be 1:

When specified to function as an output port:

The output state is determined by IO2 in the serial data.

When the data value is 0: The output state will be the open circuit state.

When the data value is 1: The output state will be a low level.

This pin is set to input mode after a power on reset.

IO2

16

Main PLL

charge pump

output

PLL charge pump output

A high level is output when the frequency of the local oscillator signal divided by N

is higher than the reference frequency, and a low level is output when that

frequency is lower. This pin goes to the high-impedance state when the

frequencies match.

PDa

20

Main PLL low-

pass filter

amplifier

transistor

Connections for the n-channel MOS transistor to be used for the PLL active low-

pass filter.

AINa

AOUTa

21

22

Continued on next page.

相关PDF资料 |

PDF描述 |

|---|---|

| LC72135M | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO20 |

| LC72136NM | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDSO24 |

| LC72140M | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDSO24 |

| LC72140 | PLL FREQUENCY SYNTHESIZER, 160 MHz, PDIP24 |

| LC72146 | PLL FREQUENCY SYNTHESIZER, 40 MHz, PDIP24 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LC72135M | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

| LC72135MA-AE | 功能描述:时钟合成器/抖动清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 输出端数量: 输出电平: 最大输出频率: 输入电平: 最大输入频率:6.1 GHz 电源电压-最大:3.3 V 电源电压-最小:2.7 V 封装 / 箱体:TSSOP-28 封装:Reel |

| LC72135MA-Q-AE | 制造商:ON Semiconductor 功能描述:PLL FREQUENCY SYNTHESIZER - Tape and Reel 制造商:ON Semiconductor 功能描述:REEL / PLL FREQUENCY SYNTHESIZER |

| LC72135M-Q-TLM-E | 制造商:SANYO Semiconductor Co Ltd 功能描述: |

| LC72136 | 制造商:SANYO 制造商全称:Sanyo Semicon Device 功能描述:PLL Frequency Synthesizer for Electronic Tuning |

发布紧急采购,3分钟左右您将得到回复。