- 您现在的位置:买卖IC网 > PDF目录16623 > LCMXO2280C-B-EVN (Lattice Semiconductor Corporation)BOARD BREAKOUT MACHXO PDF资料下载

参数资料

| 型号: | LCMXO2280C-B-EVN |

| 厂商: | Lattice Semiconductor Corporation |

| 文件页数: | 12/88页 |

| 文件大小: | 0K |

| 描述: | BOARD BREAKOUT MACHXO |

| 标准包装: | 1 |

| 系列: | MachXO |

| 主要目的: | * |

| 嵌入式: | * |

| 已用 IC / 零件: | * |

| 主要属性: | * |

| 次要属性: | * |

| 已供物品: | * |

| 其它名称: | 220-1149 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页

�� �

�

Architecture�

�MachXO� Family� Data� Sheet�

�sysCLOCK� Phase� Locked� Loops� (PLLs)�

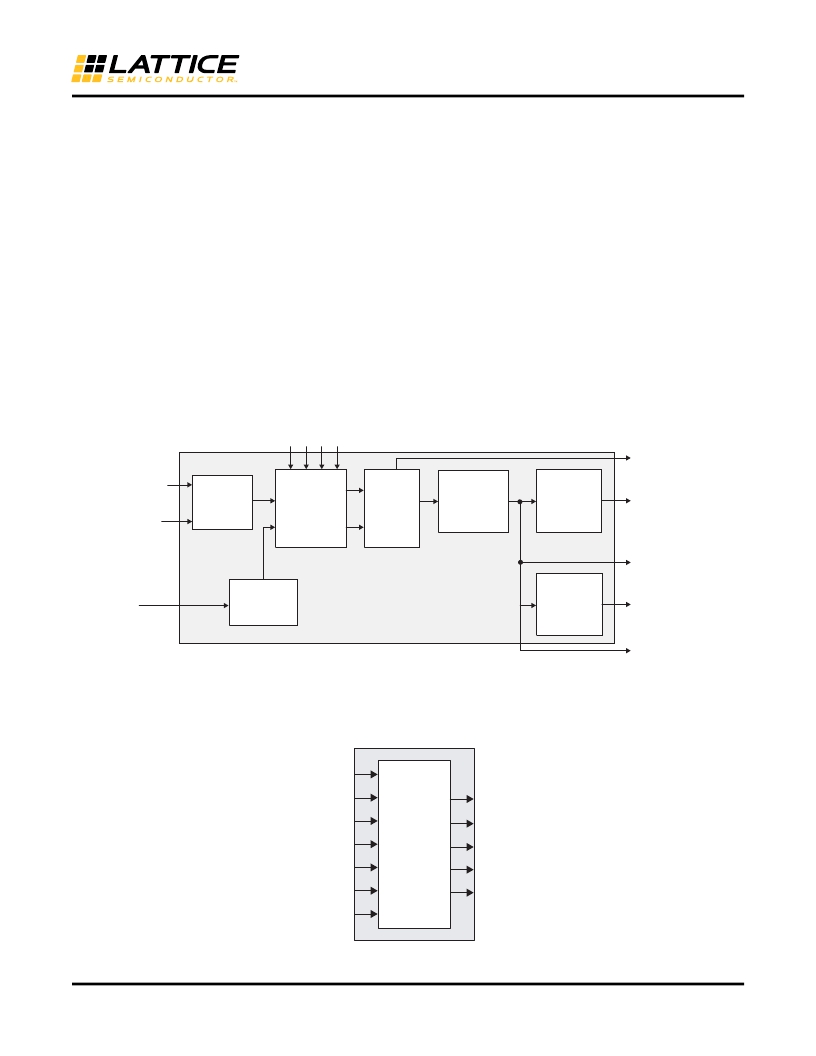

�The� MachXO1200� and� MachXO2280� provide� PLL� support.� The� source� of� the� PLL� input� divider� can� come� from� an�

�external� pin� or� from� internal� routing.� There� are� four� sources� of� feedback� signals� to� the� feedback� divider:� from�

�CLKINTFB� (internal� feedback� port),� from� the� global� clock� nets,� from� the� output� of� the� post� scalar� divider,� and� from�

�the� routing� (or� from� an� external� pin).� There� is� a� PLL_LOCK� signal� to� indicate� that� the� PLL� has� locked� on� to� the� input�

�clock� signal.� Figure� 2-10� shows� the� sysCLOCK� PLL� diagram.�

�The� setup� and� hold� times� of� the� device� can� be� improved� by� programming� a� delay� in� the� feedback� or� input� path� of�

�the� PLL� which� will� advance� or� delay� the� output� clock� with� reference� to� the� input� clock.� This� delay� can� be� either� pro-�

�grammed� during� configuration� or� can� be� adjusted� dynamically.� In� dynamic� mode,� the� PLL� may� lose� lock� after�

�adjustment� and� not� relock� until� the� t� LOCK� parameter� has� been� satisfied.� Additionally,� the� phase� and� duty� cycle� block�

�allows� the� user� to� adjust� the� phase� and� duty� cycle� of� the� CLKOS� output.�

�The� sysCLOCK� PLLs� provide� the� ability� to� synthesize� clock� frequencies.� Each� PLL� has� four� dividers� associated�

�with� it:� input� clock� divider,� feedback� divider,� post� scalar� divider,� and� secondary� clock� divider.� The� input� clock� divider�

�is� used� to� divide� the� input� clock� signal,� while� the� feedback� divider� is� used� to� multiply� the� input� clock� signal.� The� post�

�scalar� divider� allows� the� VCO� to� operate� at� higher� frequencies� than� the� clock� output,� thereby� increasing� the� fre-�

�quency� range.� The� secondary� divider� is� used� to� derive� lower� frequency� outputs.�

�Figure� 2-10.� PLL� Diagram�

�Dynamic� Delay� Adjustment�

�LOCK�

�RST�

�CLKI�

�(from� routing� or�

�Input� Clock�

�Divider�

�(CLKI)�

�Delay�

�Adjust�

�Voltage�

�VCO�

�Controlled�

�Oscillator�

�Post� Scalar�

�Divider�

�(CLKOP)�

�Phase/Duty�

�Select�

�CLKOS�

�external� pin)�

�CLKOP�

�CLKFB�

�(from� Post� Scalar�

�Divider� output,�

�Feedback�

�Divider�

�(CLKFB)�

�Secondary�

�Clock�

�Divider�

�(CLKOK)�

�CLKOK�

�clock� net,�

�routing/external�

�pin� or� CLKINTFB�

�port�

�CLKINTFB�

�(internal� feedback)�

�Figure� 2-11� shows� the� available� macros� for� the� PLL.� Table� 2-5� provides� signal� description� of� the� PLL� Block.�

�Figure� 2-11.� PLL� Primitive�

�RST�

�CLKI�

�CLKFB�

�CLKOP�

�CLKOS�

�DDA� MODE�

�DDAIZR�

�DDAILAG�

�EHXPLLC�

�CLKOK�

�LOCK�

�CLKINTFB�

�DDAIDEL[2:0]�

�2-9�

�相关PDF资料 |

PDF描述 |

|---|---|

| ELC-18B121L | COIL CHOKE 120UH RADIAL |

| GBA28DTMH | CONN EDGECARD 56POS R/A .125 SLD |

| VI-BT4-EX | CONVERTER MOD DC/DC 48V 75W |

| A6MMS-2018M | IDC CABLE - ADM20S/AE20M/ADM20S |

| HSM06DRAN | CONN EDGECARD 12POS R/A .156 SLD |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LCMXO2280C-C-EVN | 功能描述:可编程逻辑 IC 开发工具 MACHXO CNRL EVB RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| LCMXO2280C-L-EV | 功能描述:可编程逻辑 IC 开发工具 MachXO 2280C Eval Br d - Standard RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| LCMXO2280C-M-EVN | 功能描述:可编程逻辑 IC 开发工具 MachXO Mini Dev Kit RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压: |

| LCMXO2280E-3B256C | 功能描述:CPLD - 复杂可编程逻辑器件 2280 LUTs 211 I/O 1.2V -3 SPD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

| LCMXO2280E-3B256I | 功能描述:CPLD - 复杂可编程逻辑器件 2280 LUTs 211 I/O 1.2V -3 SPD RoHS:否 制造商:Lattice 系列: 存储类型:EEPROM 大电池数量:128 最大工作频率:333 MHz 延迟时间:2.7 ns 可编程输入/输出端数量:64 工作电源电压:3.3 V 最大工作温度:+ 90 C 最小工作温度:0 C 封装 / 箱体:TQFP-100 |

发布紧急采购,3分钟左右您将得到回复。