- 您现在的位置:买卖IC网 > PDF目录299411 > LP62S4096EU-70LLT (AMIC Technology Corporation) 512K X 8 BIT LOW VOLTAGE CMOS SRAM PDF资料下载

参数资料

| 型号: | LP62S4096EU-70LLT |

| 厂商: | AMIC Technology Corporation |

| 英文描述: | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| 中文描述: | 为512k × 8位低电压CMOS的SRAM |

| 文件页数: | 2/14页 |

| 文件大小: | 162K |

| 代理商: | LP62S4096EU-70LLT |

LP62S4096E-T Series

(January, 2002, Version 2.0)

10

AMIC Technology, Inc.

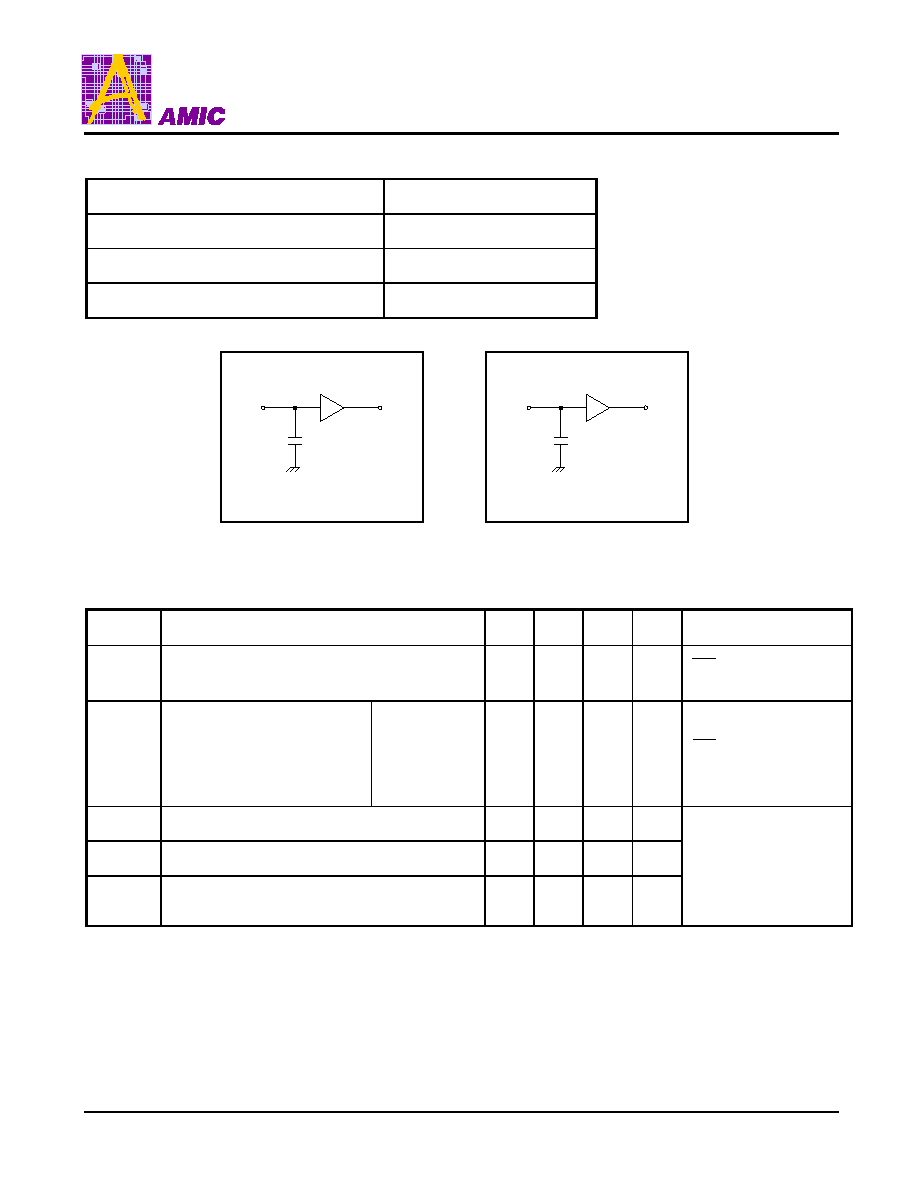

AC Test Conditions

Input Pulse Levels

0.4V to 2.4V

Input Rise and Fall Time

5 ns

Input and Output Timing Reference Levels

1.5V

Output Load

See Figures 1 and 2

30pF

* Including scope and jig.

CL

TTL

5pF

CL

TTL

Figure 1. Output Load

Figure 2. Output Load for tCLZ,

tOHZ, tOL, tCHZ, tWHZ, and tOW

Data Retention Characteristics (TA = -25

°C to 85°C)

Symbol

Parameter

Min.

Typ.

Max.

Unit

Conditions

VDR

VCC for Data Retention

2.0

-

3.6

V

CE1

≥ VCC - 0.2V, or

CE2

≤ 0.2V

VCC = 2.0V,

ICCDR

Data Retention Current

LL-Version

-

0.08

3*

A

CE1

≥ VCC - 0.2V, or

CE2

≤ 0.2V

VIN

≤ 0V

tCDR

Chip Disable to Data Retention Time

0

-

ns

tR

Operation Recovery Time

tRC

-

ns

See Retention Waveform

tVR

VCC Rising Time from Data Retention Voltage to

Operating Voltage

5

-

ms

*

LP62S4096E-55LLT / 70LLT

ICCDR: max.

1

A at TA = 0°C to + 40°C

相关PDF资料 |

PDF描述 |

|---|---|

| LP62S4096EV-55LLI | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-55LLT | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-70LLI | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EX-55LLI | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EX-55LLT | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LP62S4096EV-55LLI | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-55LLT | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-70LLI | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-70LLT | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EX-55LLI | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

发布紧急采购,3分钟左右您将得到回复。