- 您现在的位置:买卖IC网 > PDF目录299411 > LP62S4096EU-70LLT (AMIC Technology Corporation) 512K X 8 BIT LOW VOLTAGE CMOS SRAM PDF资料下载

参数资料

| 型号: | LP62S4096EU-70LLT |

| 厂商: | AMIC Technology Corporation |

| 英文描述: | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| 中文描述: | 为512k × 8位低电压CMOS的SRAM |

| 文件页数: | 6/14页 |

| 文件大小: | 162K |

| 代理商: | LP62S4096EU-70LLT |

LP62S4096E-T Series

(January, 2002, Version 2.0)

14

AMIC Technology, Inc.

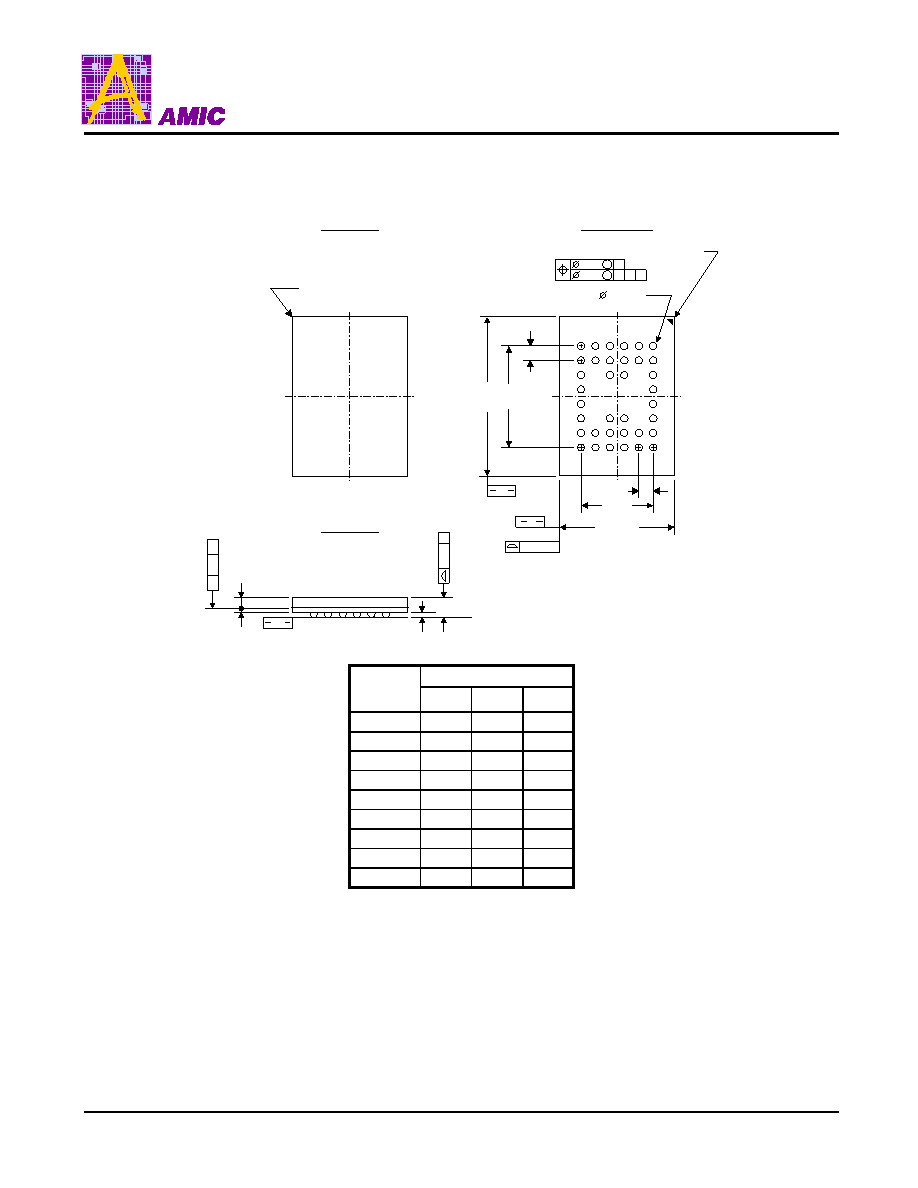

Package Information

36LD CSP (6 x 8 mm) Outline Dimensions

unit: mm

A

1

A

2

A

B

C

D

E

F

G

H

TOP VIEW

Ball#A1 CORNER

SIDE VIEW

C

SEATING PLANE

//

0.25

C

A

(0.36)

A

B

C

D

E

F

G

H

1

2

3

4

5

6

1

2

3

4

5

6

C

0.10

C

S

0.25 S

A B

b (36X)

BOTTOM VIEW

Ball*A1 CORNER

E

1

e

B

e

D1

D

A

0.20(4X)

0.10

C

Dimensions in mm

Symbol

MIN.

NOM.

MAX.

A

1.00

1.10

1.20

A1

0.16

0.21

0.26

A2

0.48

0.53

0.58

D

5.80

6.00

6.20

E

7.80

8.00

8.20

D1

---

3.75

---

E1

---

5.25

---

e

---

0.75

---

b

0.25

0.30

0.35

Note:

1. THE BALL DIAMETER, BALL PITCH, STAND-OFF & PACKAGE THICKNESS

ARE DIFFERENT FROM JEDEC SPEC MO192 (LOW PROFILE BGA FAMILY).

2. PRIMARY DATUM C AND SEATING PLANE ARE DEFINED BY THE SPHERICAL

CROWNS OF THE SOLDER BALLS.

3. DIMENSION b IS MEASURED AT THE MAXIMUM.

THEERE SHALL BE A MINIMUM CLEARANCE OF 0.25mm BETWEEN THE EDGE OF

THE SOLDER BALL AND THE BODY EDGE.

4. BALL PAD OPENING OF SUBSTRATE IS

Φ 0.25mm (SMD)

SUGGEST TO DESIGN THE PCB LAND SIZE AS

Φ 0.25mm (NSMD)

相关PDF资料 |

PDF描述 |

|---|---|

| LP62S4096EV-55LLI | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-55LLT | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-70LLI | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EX-55LLI | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EX-55LLT | 512K X 8 BIT LOW VOLTAGE CMOS SRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LP62S4096EV-55LLI | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-55LLT | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-70LLI | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EV-70LLT | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

| LP62S4096EX-55LLI | 制造商:AMICC 制造商全称:AMIC Technology 功能描述:512K X 8 BIT LOW VOLTAGE CMOS SRAM |

发布紧急采购,3分钟左右您将得到回复。