- 您现在的位置:买卖IC网 > PDF目录9218 > LTC6946IUFD-2#PBF (Linear Technology)IC INTEGER-N PLL W/VCO 28-QFN PDF资料下载

参数资料

| 型号: | LTC6946IUFD-2#PBF |

| 厂商: | Linear Technology |

| 文件页数: | 5/30页 |

| 文件大小: | 0K |

| 描述: | IC INTEGER-N PLL W/VCO 28-QFN |

| 软件下载: | PLLWizard™ PLLWizard™, with .NET 2.0 installer |

| 标准包装: | 73 |

| 类型: | 时钟/频率合成器(RF/IF),分数-N,整数-N, |

| PLL: | 是 |

| 输入: | 时钟 |

| 输出: | 时钟 |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:1 |

| 差分 - 输入:输出: | 是/是 |

| 频率 - 最大: | 4.91GHz |

| 除法器/乘法器: | 是/是 |

| 电源电压: | 3.15 V ~ 5.25 V |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 28-WFQFN 裸露焊盘 |

| 供应商设备封装: | 28-QFN(4x5) |

| 包装: | 管件 |

第1页第2页第3页第4页当前第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页

LTC6946

13

6946fa

divide ratio. See the Applications Information section for

the relationship between R and the fREF, fPFD, fVCO and

fRF frequencies.

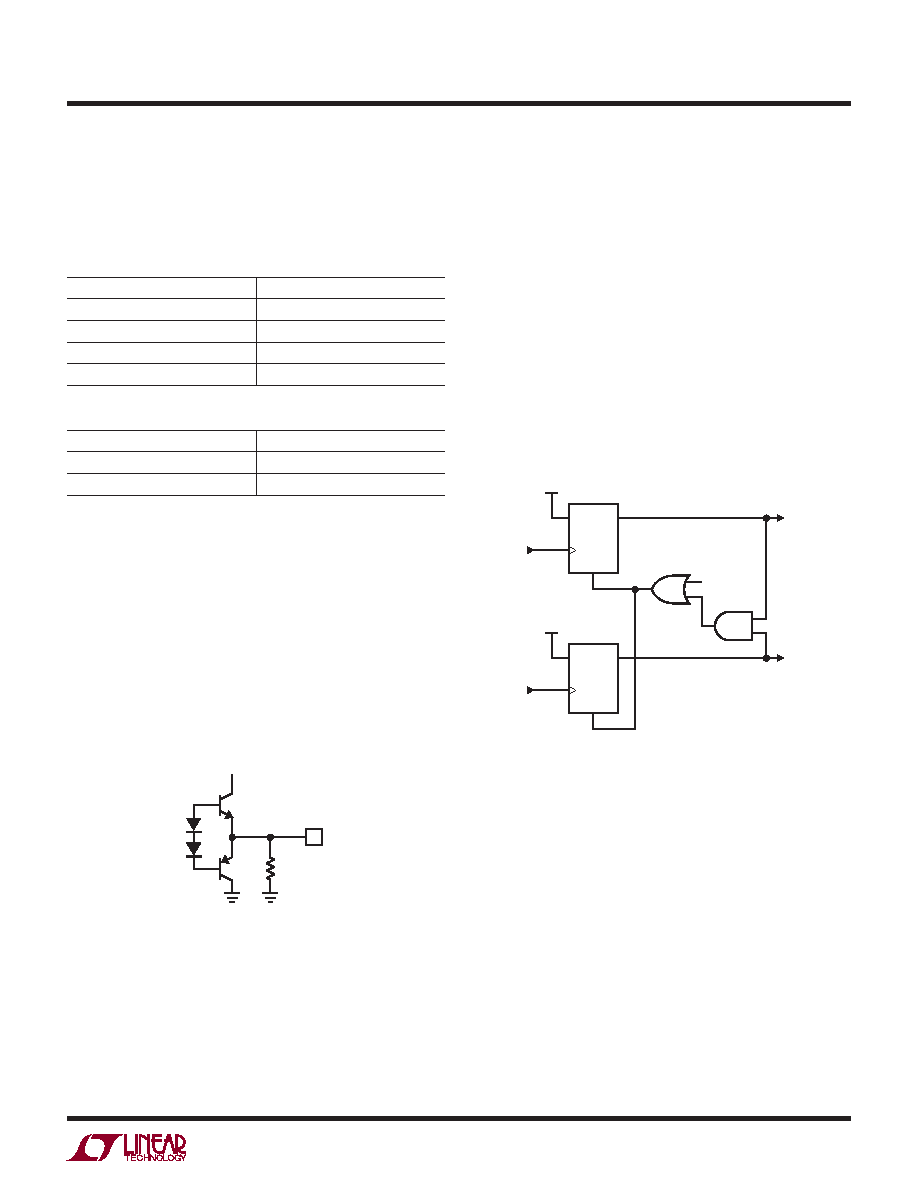

PHASE/FREQUENCY DETECTOR (PFD)

The phase/frequency detector (PFD), in conjunction with

the charge pump, produces source and sink current pulses

proportional to the phase difference between the outputs

of the R and N dividers. This action provides the necessary

feedback to phase-lock the loop, forcing a phase align-

ment at the PFD’s inputs. The PFD may be disabled with

the CPRST bit which prevents UP and DOWN pulses from

being produced. See Figure 3 for a simplified schematic

of the PFD.

The BST bit should be set based upon the input signal level

to prevent the reference input buffer from saturating. See

Table 2 for recommended settings and the Applications

Information section for programming examples.

Table 1. FILT[1:0] Programming

FILT[1:0]

fREF

3

<20MHz

2NA

1

20MHz to 50MHz

0

>50MHz

Table 2. BST Programming

BST

VREF

1

<2.0VP-P

0

≥2.0VP-P

REFERENCE OUTPUT BUFFER

The reference output buffer produces a low noise square

wave with a noise floor of –155dBc/Hz (typical) at 10MHz.

Its output is low impedance, and produces 0dBm typical

output power into a 50Ω load at 10MHz. Larger output

swings will result if driving larger impedances. The out-

put is self-biased, and must be AC-coupled with a 22nF

capacitor (see Figure 2 for a simplified schematic). The

buffer may be powered down by using bit PDREFO found

in the serial port Power register h02.

2

REFO

VREFO

+

800Ω

6946 F02

Figure 2. Simplified REFO Interface Schematic

OPERATION

DQ

RST

N DIV

DQ

RST

CPRST

UP

DOWN

6946 F03

DELAY

R DIV

Figure 3. Simplified PFD Schematic

REFERENCE (R) DIVIDER

A 10-bit divider, R_DIV, is used to reduce the frequency

seen at the PFD. Its divide ratio R may be set to any

integer from 1 to 1023, inclusive. Use the RD[9:0] bits

found in registers h03 and h04 to directly program the R

LOCK INDICATOR

The lock indicator uses internal signals from the PFD to

measure phase coincidence between the R and N divider

output signals. It is enabled by setting the LKEN bit in

the serial port register h07, and produces both LOCK and

UNLOCK status flags, available through both the STAT

output and serial port register h00.

The user sets the phase difference lock window time,

tLWW, for a valid LOCK condition with the LKWIN[1:0] bits.

See Table 3 for recommended settings for different FPFD

frequencies and the Applications Information section for

examples.

相关PDF资料 |

PDF描述 |

|---|---|

| VI-B44-IU-B1 | CONVERTER MOD DC/DC 48V 200W |

| SY89429AJZ | IC SYNTHESIZER FREQ PROGR 28PLCC |

| SY58038UMY TR | IC MUX 8:1 PREC 1:2 LVPECL 44MLF |

| X9317WS8IZ-2.7 | IC XDCP SGL 100TAP 10K 8-SOIC |

| AD9514BCPZ | IC CLOCK DIST 3OUT PLL 32LFCSP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| LTC6946IUFD-3#PBF | 功能描述:IC INTEGER-N PLL W/VCO 28-QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 频率合成器 PLL:是 输入:晶体 输出:时钟 电路数:1 比率 - 输入:输出:1:1 差分 - 输入:输出:无/无 频率 - 最大:1GHz 除法器/乘法器:是/无 电源电压:4.5 V ~ 5.5 V 工作温度:-20°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-LSSOP(0.175",4.40mm 宽) 供应商设备封装:16-SSOP 包装:带卷 (TR) 其它名称:NJW1504V-TE1-NDNJW1504V-TE1TR |

| LTC6946IUFD-3#TRPBF | 功能描述:IC INTEGER-N PLL W/VCO 28QFN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:1,000 系列:Precision Edge® 类型:时钟/频率合成器 PLL:无 输入:CML,PECL 输出:CML 电路数:1 比率 - 输入:输出:2:1 差分 - 输入:输出:是/是 频率 - 最大:10.7GHz 除法器/乘法器:无/无 电源电压:2.375 V ~ 3.6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:16-VFQFN 裸露焊盘,16-MLF? 供应商设备封装:16-MLF?(3x3) 包装:带卷 (TR) 其它名称:SY58052UMGTRSY58052UMGTR-ND |

| LTC6946-x | 制造商:LINER 制造商全称:Linear Technology 功能描述:16-Bit, 20Msps Low Noise Dual ADC |

| LTC694C | 制造商:LINER 制造商全称:Linear Technology 功能描述:Microprocessor Supervisory Circuits |

| LTC694C-3.3 | 制造商:LINER 制造商全称:Linear Technology 功能描述:3.3V Microprocessor Supervisory Circuits |

发布紧急采购,3分钟左右您将得到回复。