- 您现在的位置:买卖IC网 > PDF目录69012 > M35080FP 128 X 96 DOTS CRT CHAR OR GRPH DSPL CTLR, PDSO24 PDF资料下载

参数资料

| 型号: | M35080FP |

| 元件分类: | 显示控制器 |

| 英文描述: | 128 X 96 DOTS CRT CHAR OR GRPH DSPL CTLR, PDSO24 |

| 封装: | 0.300 INCH, 0.80 MM PITCH, SSOP-24 |

| 文件页数: | 28/30页 |

| 文件大小: | 304K |

| 代理商: | M35080FP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页当前第28页第29页第30页

MITSUBISHI MICROCOMPUTERS

M35080FP

SCREEN CHARACTER and PATTERN DISPLAY CONTROLLERS

4

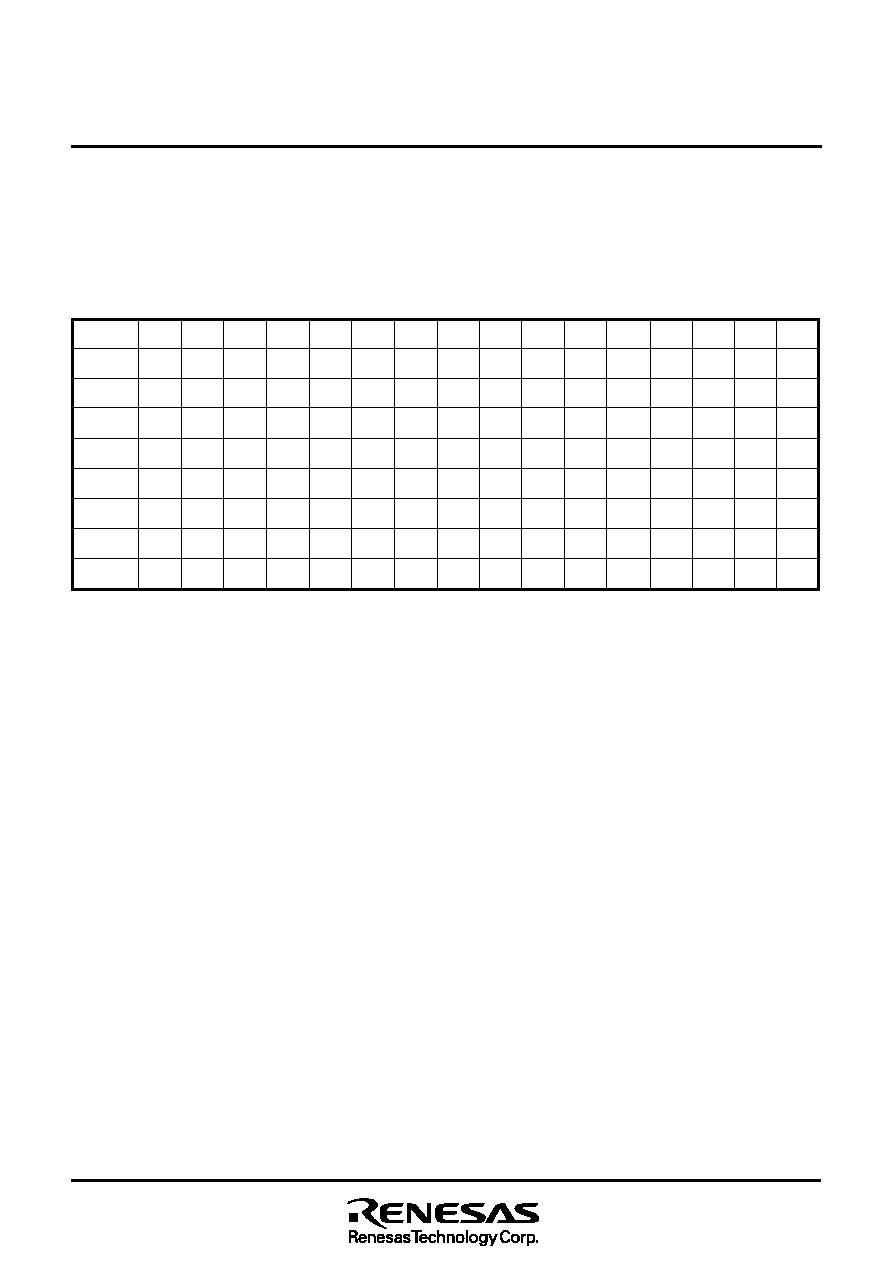

MEMORY CONSTITUTION

Address 000016 to 000716 are assigned to the display RAM, ad-

dress 100016 to 3AFF16 are assigned to bitmap RAM. The internal

circuit is reset and all display control registers (address 000016 to

000716) are set to "0" when the AC pin level is "L". And then, bit

map RAM is not erased and be undefinited. This memory has 2-

page composition (an address is Page A and page B community)

Fig.1 Memory constitution (Display Control register)

DAF

DAE

DAD

DAC

DAB

DAA

DA9

DA8

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

–

––––

–

PAGEONB PAGEONA

–

––––

YM2

YM1

YM0 BLANK1 BLANK0 ALLON DSPON

–

WIDTH2 WIDTH1 WIDTH0

–

VSIZE1 VSIZE0

––

–

VP9

VP8

VP7

VP6

VP5

VP4

VP3

VP2

VP1

VP0

–

––––

–

HP9

HP8

HP7

HP6

HP5

HP4

HP3

HP2

HP1

HP0

–

ANADIG2 ANADIG1 ANADIG0 SYNCCK

TEST

–––

––

POLV POLH MODE2 MODE1 MODE0

–

––––

–––

–

DACON

–––

––––

–––

–

––––

–––

SBLANK3 SBLANK2 SBLANK1 SBLANK0

PTD3

PTD2

PTD1

PTD0

000016

000116

000216

000316

000416

000516

000616

000716

Address

of the memory for page A, and the memory for page B. Registers

PAGEONA and PAGEONB perform page control at the time of

writing in data. For detail, refer to "DATA INPUT EXAMPLE".

Memory constitution is shown in Figure 1 to 10.

Note : Address 000016 and 000416 to 000716 are Page A and B common registers. The writing of data is made regardless of registers PAGEONA and

PAGEONB. As for addresses 000116 to 000316, register of Page A and Page B exists for every page (common to an address.)

When write data in the memory for page A, and write data in the memory for page B, set it as register PAGEONA = “1” at register PAGEONB = “1.”

When both of PAGEONA and PAGEONB are set to “1”, data can be simultaneously written in both the memory for page A, and the memory for page B.

Address 0XXX16 other than addresses 000016 to 000716 are write-protected.

相关PDF资料 |

PDF描述 |

|---|---|

| M35500BGP | FLUORESCENT DSPL CTRL, PQFP44 |

| M35500AFP | FLUORESCENT DSPL CTRL, PQFP44 |

| M37150M8-XXXFP | 8-BIT, MROM, 8.95 MHz, MICROCONTROLLER, PDSO42 |

| M37150MF-XXXFP | 8-BIT, MROM, 8.95 MHz, MICROCONTROLLER, PDSO42 |

| M37150EFFP | 8-BIT, OTPROM, 8.95 MHz, MICROCONTROLLER, PDSO42 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M35080MN | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8 Kbit Serial SPI Bus EEPROM With Incremental Registers |

| M35080-MN3T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8 Kbit Serial SPI Bus EEPROM With Incremental Registers |

| M35080-MN6T | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:8 Kbit Serial SPI Bus EEPROM With Incremental Registers |

| M350X30MMN70 | 制造商:n/a 功能描述:Ships in 2 days |

| M3-51 | 制造商:Southco 功能描述: |

发布紧急采购,3分钟左右您将得到回复。