- 您现在的位置:买卖IC网 > PDF目录80550 > M38D5XGXHP 8-BIT, FLASH, 6.25 MHz, MICROCONTROLLER, PQFP80 PDF资料下载

参数资料

| 型号: | M38D5XGXHP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, FLASH, 6.25 MHz, MICROCONTROLLER, PQFP80 |

| 封装: | 12 X 12 MM, 0.50 MM PITCH, PLASTIC, LQFP-80 |

| 文件页数: | 85/142页 |

| 文件大小: | 2004K |

| 代理商: | M38D5XGXHP |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页当前第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页

Rev.3.04

May 20, 2008

REJ03B0158-0304

38D5 Group

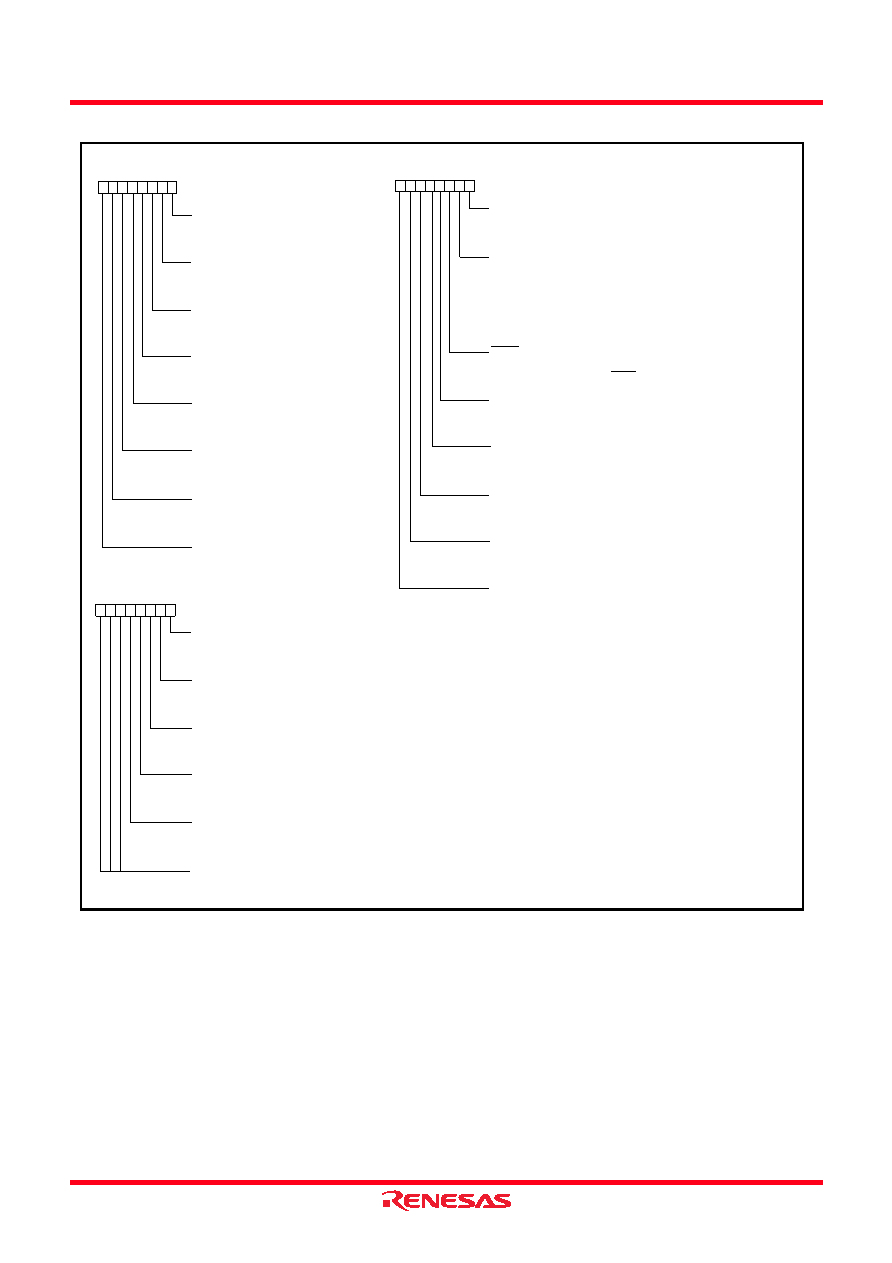

Fig. 37 Structure of serial I/O1 related registers

b7

b0

b7

b0

b7

b0

BRG count source selection bit (CSS)

0:

φSOURCE

1:

φSOURCE/4

Serial I/O1 synchronous clock selection bit (SCS)

0: BRG output divided by 4 when clock synchronous

serial I/O is selected.

BRG output divided by 16 when UART is selected.

1: External clock input when clock synchronous serial

I/O is selected.

External clock input divided by 16 when UART is selected.

SRDY1 output enable bit (SRDY)

0: P43 pin operates as ordinary I/O pin

1: P43 pin operates as SRDY1 output pin

Transmit interrupt source selection bit (TIC)

0: Interrupt when transmit buffer has emptied

1: Interrupt when transmit shift operation is completed

Transmit enable bit (TE)

0: Transmit disabled

1: Transmit enabled

Receive enable bit (RE)

0: Receive disabled

1: Receive enabled

Serial I/O1 mode selection bit (SIOM)

0: Clock asynchronous (UART) serial I/O

1: Clock synchronous serial I/O

Serial I/O1 enable bit (SIOE)

0: Serial I/O1 disabled

(pins P40 to P43 operate as ordinary I/O pins)

1: Serial I/O1 enabled

(pins P40 to P43 operate as serial I/O pins)

Transmit buffer empty flag (TBE)

0: Buffer full

1: Buffer empty

Receive buffer full flag (RBF)

0: Buffer empty

1: Buffer full

Transmit shift completion flag (TSC)

0: Transmit shift in progress

1: Transmit shift completed

Overrun error flag (OE)

0: No error

1: Overrun error

Parity error flag (PE)

0: No error

1: Parity error

Framing error flag (FE)

0: No error

1: Framing error

Summing error flag (SE)

0: (OE) U (PE) U (FE)=0

1: (OE) U (PE) U (FE)=1

Not used (returns “1” when read)

Serial I/O1 control register

(SIO1CON : address 001A16)

Serial I/O1 status register

(SIO1STS : address 001916)

Character length selection bit (CHAS)

0: 8 bits

1: 7 bits

Parity enable bit (PARE)

0: Parity checking disabled

1: Parity checking enabled

Parity selection bit (PARS)

0: Even parity

1: Odd parity

Stop bit length selection bit (STPS)

0: 1 stop bit

1: 2 stop bits

P41/TXD P-channel output disable bit (POFF)

0: CMOS output (in output mode)

1: N-channel open drain output (in output mode)

Not used (return “1” when read)

UART control register

(UARTCON : address 001B16)

(1)

Note1:

φSOURCE indicates the followings:

XIN input in the frequency/2, 4, or 8 mode

On-chip oscillator divided by 4 in the on-chip oscillator mode

Sub-clock in the low-speed mode

相关PDF资料 |

PDF描述 |

|---|---|

| MC9328MX21SVK | 32-BIT, 266 MHz, MICROPROCESSOR, PBGA289 |

| MK3724GLFTR | 73.728 MHz, OTHER CLOCK GENERATOR, PDSO16 |

| MB95F136TSPFV | 8-BIT, FLASH, 10 MHz, MICROCONTROLLER, PDSO28 |

| MB95F353EPFT-G-SNE2 | MICROCONTROLLER, PDSO24 |

| MB95F353LWQN-G-SNERE1 | MICROCONTROLLER, PQCC32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M38DC-15 | 制造商:M/A-COM Technology Solutions 功能描述:MIXER(SPEC UX1015) - Bulk |

| M38K00F1-16FP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38K00F1-16HP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38K00F1-32FP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M38K00F1-32HP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

发布紧急采购,3分钟左右您将得到回复。