- 您现在的位置:买卖IC网 > PDF目录45049 > M41ST87YWX6 (STMICROELECTRONICS) 1 TIMER(S), REAL TIME CLOCK, PDSO28 PDF资料下载

参数资料

| 型号: | M41ST87YWX6 |

| 厂商: | STMICROELECTRONICS |

| 元件分类: | 时钟/数据恢复及定时提取 |

| 英文描述: | 1 TIMER(S), REAL TIME CLOCK, PDSO28 |

| 封装: | 0.300 INCH, PLASTIC, SO-28 |

| 文件页数: | 3/38页 |

| 文件大小: | 569K |

| 代理商: | M41ST87YWX6 |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

11/38

M41ST87Y, M41ST87W

Data Valid. The state of the data line represents

valid data when after a start condition, the data line

is stable for the duration of the high period of the

clock signal. The data on the line may be changed

during the Low period of the clock signal. There is

one clock pulse per bit of data.

Each data transfer is initiated with a start condition

and terminated with a stop condition. The number

of data bytes transferred between the start and

stop conditions is not limited. The information is

transmitted byte-wide and each receiver acknowl-

edges with a ninth bit.

By definition a device that gives out a message is

called “transmitter,” the receiving device that gets

the message is called “receiver.” The device that

controls the message is called “master.” The de-

vices that are controlled by the master are called

“slaves.”

Acknowledge. Each byte of eight bits is followed

by one Acknowledge Bit. This Acknowledge Bit is

a low level put on the bus by the receiver whereas

the master generates an extra acknowledge relat-

ed clock pulse. A slave receiver which is ad-

dressed is obliged to generate an acknowledge

after the reception of each byte that has been

clocked out of the slave transmitter.

The device that acknowledges has to pull down

the SDA line during the acknowledge clock pulse

in such a way that the SDA line is a stable Low dur-

ing the High period of the acknowledge related

clock pulse. Of course, setup and hold times must

be taken into account. A master receiver must sig-

nal an end of data to the slave transmitter by not

generating an acknowledge on the last byte that

has been clocked out of the slave. In this case the

transmitter must leave the data line High to enable

the master to generate the STOP condition.

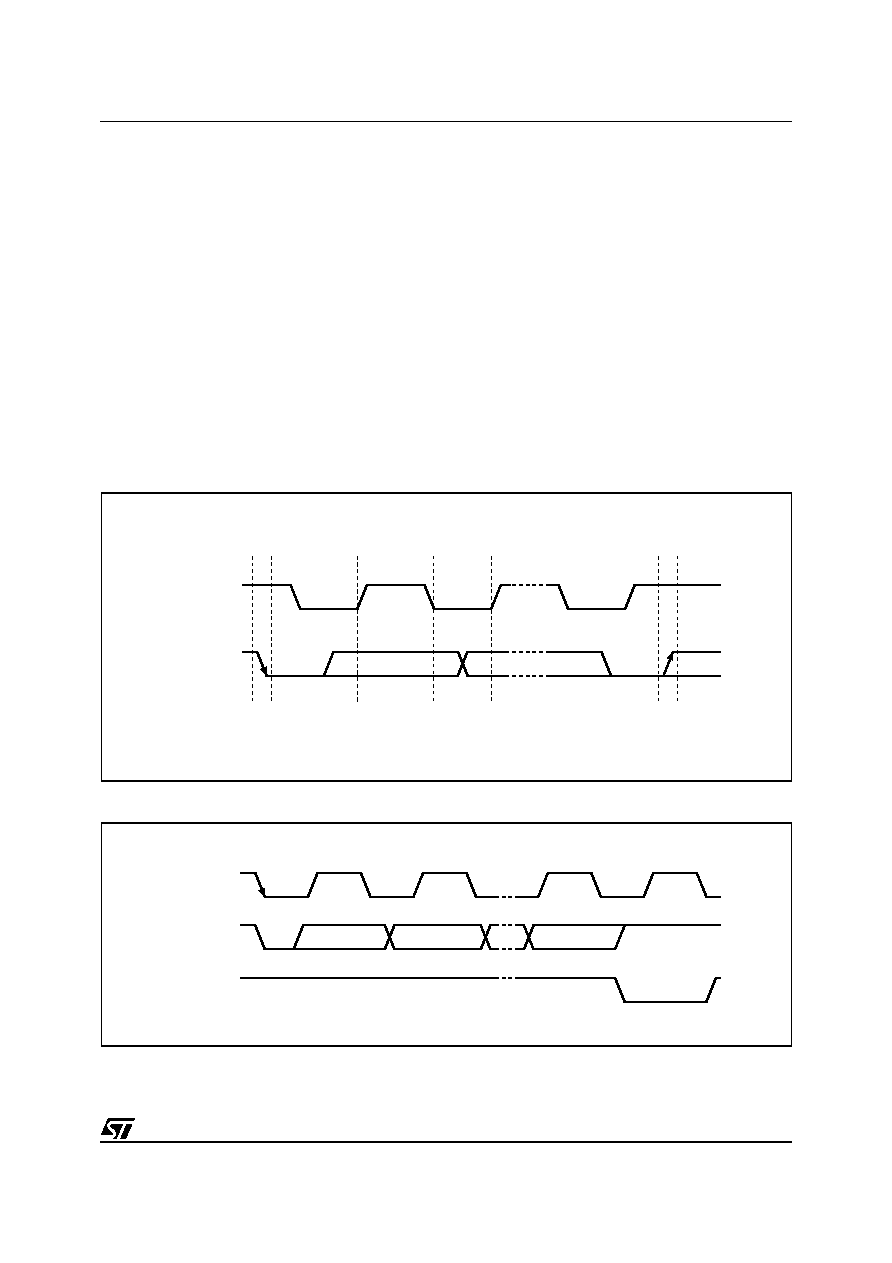

Figure 7. Serial Bus Data Transfer Sequence

Figure 8. Acknowledgement Sequence

AI00587

DATA

CLOCK

DATA LINE

STABLE

DATA VALID

START

CONDITION

CHANGE OF

DATA ALLOWED

STOP

CONDITION

AI00601

DATA OUTPUT

BY RECEIVER

DATA OUTPUT

BY TRANSMITTER

SCL FROM

MASTER

START

CLOCK PULSE FOR

ACKNOWLEDGEMENT

12

89

MSB

LSB

相关PDF资料 |

PDF描述 |

|---|---|

| M41T00M6F | REAL TIME CLOCK, PDSO8 |

| M41T00M6E | REAL TIME CLOCK, PDSO8 |

| M41T00M6 | 0 TIMER(S), REAL TIME CLOCK, PDSO8 |

| M41T0DS6 | REAL TIME CLOCK, PDSO8 |

| M41T0DS6T | REAL TIME CLOCK, PDSO8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M41ST95W | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.0V, 512 bit (64 bit X 8) Serial RTC (SPI) SRAM and NVRAM Supervisor |

| M41ST95WMH6 | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.0V, 512 bit (64 bit X 8) Serial RTC (SPI) SRAM and NVRAM Supervisor |

| M41ST95WMH6E | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.0V, 512 bit (64 bit X 8) Serial RTC (SPI) SRAM and NVRAM Supervisor |

| M41ST95WMH6F | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.0V, 512 bit (64 bit X 8) Serial RTC (SPI) SRAM and NVRAM Supervisor |

| M41ST95WMH6TR | 制造商:STMICROELECTRONICS 制造商全称:STMicroelectronics 功能描述:5.0 or 3.0V, 512 bit (64 bit X 8) Serial RTC (SPI) SRAM and NVRAM Supervisor |

发布紧急采购,3分钟左右您将得到回复。