- 您现在的位置:买卖IC网 > PDF目录383300 > M470L6423CK0 (SAMSUNG SEMICONDUCTOR CO. LTD.) 512MB DDR SDRAM MODULE (64Mx64 based on DDP 64Mx 8 DDR SDRAM) 200pin SODIMM 64bit Non-ECC/Parity PDF资料下载

参数资料

| 型号: | M470L6423CK0 |

| 厂商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 512MB DDR SDRAM MODULE (64Mx64 based on DDP 64Mx 8 DDR SDRAM) 200pin SODIMM 64bit Non-ECC/Parity |

| 中文描述: | 512MB的DDR SDRAM内存模组(64Mx64基于铂64Mx 8 DDR内存)200pin的SODIMM 64 Non-ECC/Parity |

| 文件页数: | 10/14页 |

| 文件大小: | 121K |

| 代理商: | M470L6423CK0 |

200pin DDR SDRAM SODIMM

M470L6423CK0

Rev. 0.0 Aug. 2001

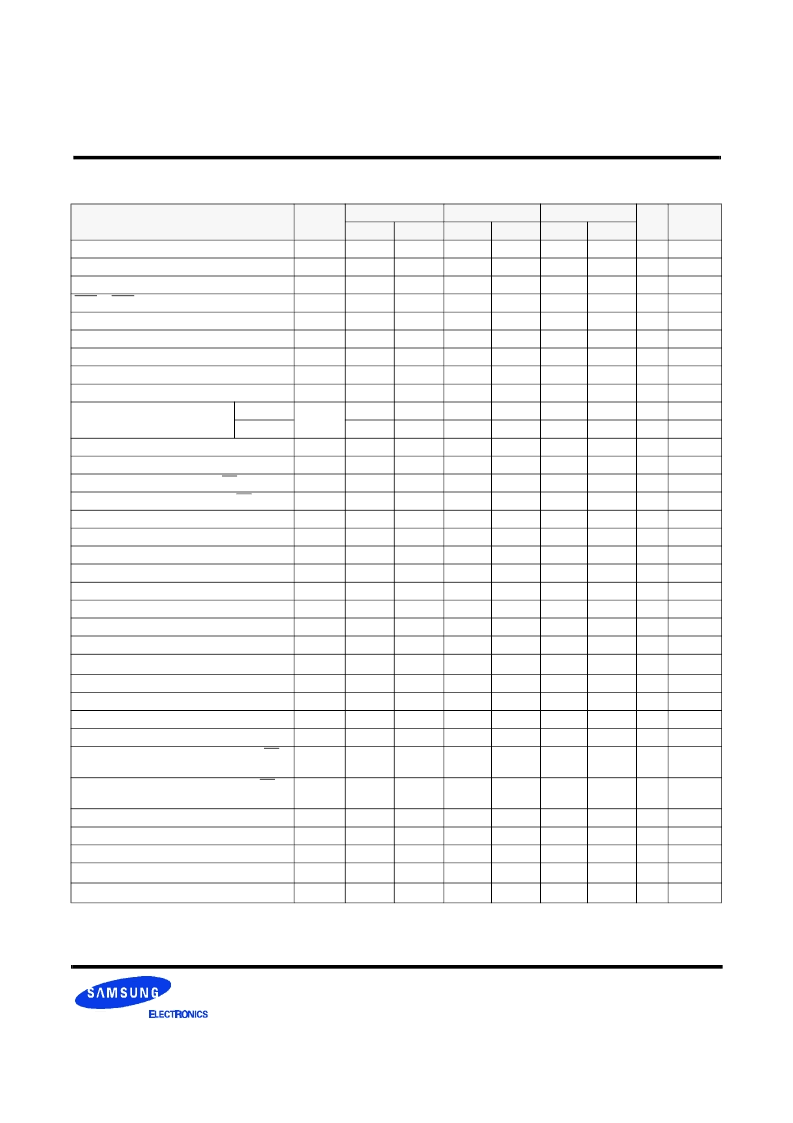

AC Timming Parameters & Specifications

(These AC charicteristics were tested on the Component)

-TCA2(DDR266A) -TCB0(DDR266B)

Parameter

Symbol

-TCA0 (DDR200)

Unit

Note

Min

Max

Min

Max

Min

Max

Row cycle time

tRC

65

65

70

ns

Refresh row cycle time

tRFC

75

75

80

ns

Row active time

tRAS

45

120K

45

120K

48

120K

ns

RAS to CAS delay

tRCD

20

20

20

ns

Row precharge time

tRP

20

20

20

ns

Row active to Row active delay

tRRD

15

15

15

ns

Write recovery time

tWR

2

2

2

tCK

Last data in to Read command

tCDLR

1

1

1

tCK

Col. address to Col. address delay

tCCD

1

1

1

tCK

Clock cycle time

CL=2.0

tCK

7.5

12

10

12

10

12

ns

5

CL=2.5

7.5

12

7.5

12

12

ns

5

Clock high level width

tCH

0.45

0.55

0.45

0.55

0.45

0.55

tCK

Clock low level width

tCL

0.45

0.55

0.45

0.55

0.45

0.55

tCK

DQS-out access time from CK/CK

tDQSCK

-0.75

+0.75

-0.75

+0.75

-0.8

+0.8

ns

Output data access time from CK/CK

tAC

-0.75

+0.75

-0.75

+0.75

-0.8

+0.8

ns

Data strobe edge to ouput data edge

tDQSQ

-

+0.5

-

+0.5

-

+0.6

ns

5

Read Preamble

tRPRE

0.9

1.1

0.9

1.1

0.9

1.1

tCK

Read Postamble

tRPST

0.4

0.6

0.4

0.6

0.4

0.6

tCK

CK to valid DQS-in

tDQSS

0.75

1.25

0.75

1.25

0.75

1.25

tCK

DQS-in setup time

tWPRES

0

0

0

ns

2

DQS-in hold time

tWPREH

0.25

0.25

0.25

tCK

DQS falling edge to CK rising-setup time

tDSS

0.2

0.2

0.2

tCK

DQS falling edge from CK rising-hold time

tDSH

0.2

0.2

0.2

tCK

DQS-in high level width

tDQSH

0.35

0.35

0.35

tCK

DQS-in low level width

tDQSL

0.35

0.35

0.35

tCK

DQS-in cycle time

tDSC

0.9

1.1

0.9

1.1

0.9

1.1

tCK

Address and Control Input setup time

tIS

0.9

0.9

1.1

ns

6

Address and Control Input hold time

tIH

0.9

0.9

1.1

ns

6

Data-out high impedence time from CK/CK

tHZ

tACmin -

400ps

tACmax

- 400ps

tACmin

- 400ps

tACmax

- 400ps

tACmin

- 400ps

tACmax

- 400ps

ps

Data-out low impedence time from CK/CK

tLZ

tACmin -

400ps

tACmax

- 400ps

tACmin

- 400ps

tACmax

- 400ps

tACmin

- 400ps

tACmax

- 400ps

ps

Input Slew Rate(for input only pins)

tSL(I)

0.5

0.5

0.5

V/ns

6

Input Slew Rate(for I/O pins)

tSL(IO)

0.5

0.5

0.5

V/ns

7

Output Slew Rate(x4,x8)

tSL(O)

1.0

4.5

1.0

4.5

1.0

4.5

V/ns

10

Output Slew Rate(x16)

tSL

(O)

0.7

5

0.7

5

0.7

5

V/ns

10

Output Slew Rate Matching Ratio(rise to fall)

t

SLMR

0.67

1.5

0.67

1.5

0.67

1.5

相关PDF资料 |

PDF描述 |

|---|---|

| M470L6423EN | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-A2 | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-B0 | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CB3 | 512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CLB3 | 512MB Unbuffered SODIMM(based on sTSOP) |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M470L6423EN | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-A2 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-B0 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CB3 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

| M470L6423EN0-CLB3 | 制造商:SAMSUNG 制造商全称:Samsung semiconductor 功能描述:512MB Unbuffered SODIMM(based on sTSOP) |

发布紧急采购,3分钟左右您将得到回复。