- 您现在的位置:买卖IC网 > PDF目录383305 > M5M5Y5672TG-25 (Mitsubishi Electric Corporation) 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM PDF资料下载

参数资料

| 型号: | M5M5Y5672TG-25 |

| 厂商: | Mitsubishi Electric Corporation |

| 英文描述: | 18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM |

| 中文描述: | 18874368位(262144 - Word的72位)网络的SRAM |

| 文件页数: | 12/27页 |

| 文件大小: | 240K |

| 代理商: | M5M5Y5672TG-25 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页当前第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页

MITSUBISHI LSIs

M5M5Y5672TG – 25,22,20

18874368-BIT(262144-WORD BY 72-BIT) NETWORK SRAM

12

MITSUBISHI

ELECTRIC

Advanced Information

M5M5Y5672TG REV.0.1

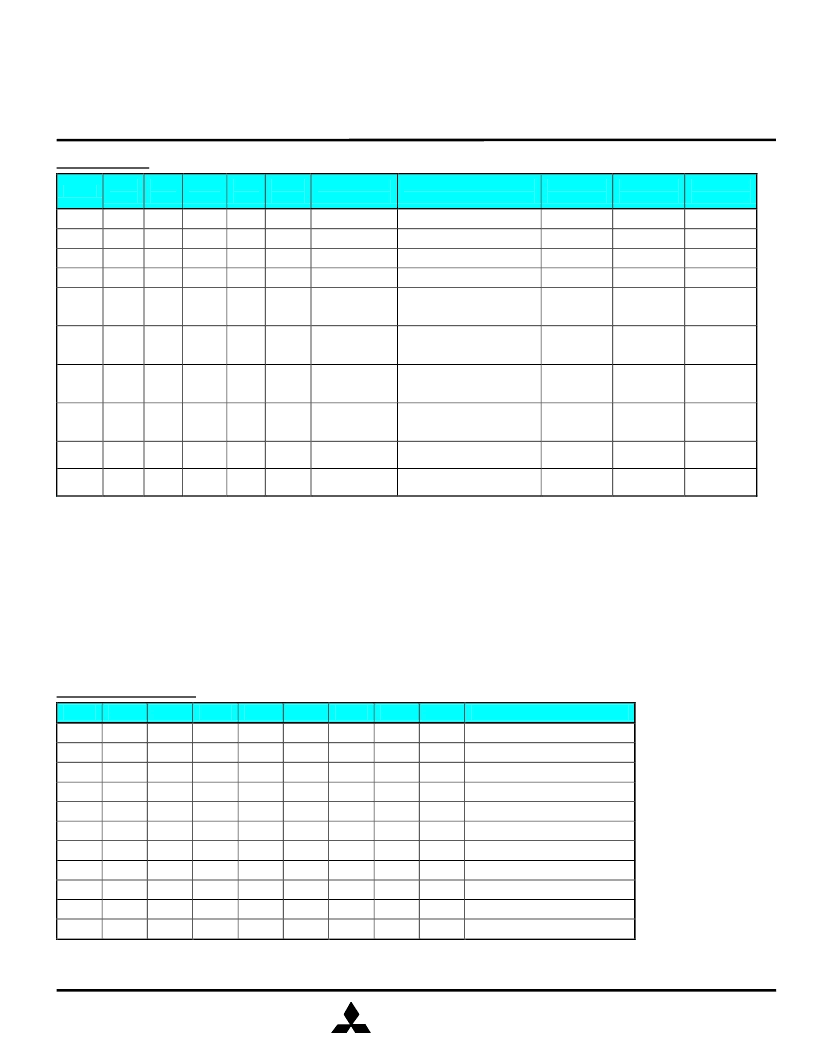

TRUTH TABLE

CLK

E1#

(t

n

)

E

(t

n

)

ADV

(t

n

)

W#

(t

n

)

BW#

(t

n

)

Previous

Operation

Current

Operation

DQ/CQ

(t

n

)

DQ/CQ

(t

n+1

)

DQ/CQ

(t

n+2

)

L->H

X

X

H

X

F

X

T

X

L

H

L

H

X

X

X

X

X

X

X

X

X

Bank Deselect

***

High-Z

---

---

---

---

L->H

L->H

L->H

Bank Deselect

X

Bank Deselect (Continue)

High-Z

***

High-Z / CQ

High-Z

Deselect

High-Z / CQ

Deselect

Deselect (Continue)

Write

Loads new address

Stores DQx if BWx#=LOW

Write (Abort)

Loads new address

No data stored

Write Continue

Increments address by 1

Stores DQx if BWx#=LOW

Write Continue (Abort)

Increments address by 1

No data stored

Read

Loads new address

Read Continue

Increments address by 1

High-Z / CQ

L->H

L

T

L

L

T

X

***

***

D

n

/ CQ

(t

n

)

L->H

L

T

L

L

F

X

***

***

High-Z / CQ

L->H

X

X

H

X

T

Write

***

D

n-1

/ CQ

(t

n-1

)

D

n

/ CQ

(t

n

)

L->H

X

X

H

X

F

Write

***

D

n-1

/ CQ

(t

n-1

)

High-Z / CQ

L->H

L

T

L

H

X

X

***

Q

n

/ CQ

(t

n

)

Q

n

/ CQ

(t

n

)

---

L->H

X

X

H

X

X

Read

Q

n-1

/ CQ

(t

n-1

)

---

Note11. If E2=EP2 and E3=EP3 then E=”T” else E=”F”.

Note12. If one or more BWx#=LOW then BW#=”T” else BW#=”F”.

Note13. “H” = input “HIGH”; “L” = input “LOW”; “X” = input “don’t care”; “T” = input “true”; “F” = input “false”.

Note14. “ *** “ = indicates that the DQ input requirement / output state and CQ output state are determined by the previous operation.

Note15. “ --- “ = indicates that the DQ input requirement / output state and CQ output state are determined by the next operation.

Note16. DQs are tri-stated in response to Bank Deselect, Deselect and Write commands, one full cycle after the command is sampled.

Note17. CQs are tri-stated in response to Bank Deselect commands only, one full cycle after the command is sampled.

Note18. Up to three (3) Continue operations may be initiated after a Read or Write operation is initiated to burst transfer up to four (4)

distinct pieces of data per single external address input. If a fourth (4) Continue operation is initiated, the internal address

wraps back to the initial external (base) address.

WRITE TRUTH TABLE

W#

BWa#

BWb#

BWc#

BWd#

BWe#

X

H

H

H

H

L

H

H

H

L

H

BWf#

X

H

H

H

H

H

L

H

H

L

H

BWg#

X

H

H

H

H

H

H

L

H

L

H

BWh#

X

H

H

H

H

H

H

H

L

L

H

Function

H

L

L

L

L

L

L

L

L

L

L

X

L

H

H

H

H

H

H

H

L

H

X

H

L

H

H

H

H

H

H

L

H

X

H

H

L

H

H

H

H

H

L

H

X

H

H

H

L

H

H

H

H

L

H

Read

Write Byte “a”

Write Byte “b”

Write Byte “c”

Write Byte “d”

Write Byte “e”

Write Byte “f”

Write Byte “g”

Write Byte “h”

Write All Bytes

Write Abort / NOP

Note19. X means "don't care". H means logic HIGH. L means logic LOW.

Note20. All inputs must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

相关PDF资料 |

PDF描述 |

|---|---|

| M5M5Y816WG-70HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M5Y816WG-85HI | 8388608-BIT (524288-WORD BY 16-BIT) CMOS STATIC RAM |

| M5M82C59AFP | The M5M82C59AFP,-2 is programmable LSI Interupt control |

| M5M82C59AFP-2 | The M5M82C59AFP,-2 is programmable LSI Interupt control |

| M5M82C59AP | The M5M82C59AP,-2 is programmable LSI Interupt control |

相关代理商/技术参数 |

参数描述 |

|---|---|

| M5M80011A | 制造商:Mitsubishi Electric 功能描述: |

| M5M82C54P | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:CMOS PROGRAMMABLE INTERVAL TIMER |

| M5M82C54P-6 | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:CMOS PROGRAMMABLE INTERVAL TIMER |

| M5M82C55AFP2 | 制造商:Panasonic Industrial Company 功能描述:IC |

| M5M82C59AFP | 制造商:MITSUBISHI 制造商全称:Mitsubishi Electric Semiconductor 功能描述:The M5M82C59AFP,-2 is programmable LSI Interupt control |

发布紧急采购,3分钟左右您将得到回复。