- 您现在的位置:买卖IC网 > PDF目录180471 > MACH111SP-5VC (LATTICE SEMICONDUCTOR CORP) High-Performance EE CMOS Programmable Logic PDF资料下载

参数资料

| 型号: | MACH111SP-5VC |

| 厂商: | LATTICE SEMICONDUCTOR CORP |

| 元件分类: | PLD |

| 英文描述: | High-Performance EE CMOS Programmable Logic |

| 中文描述: | EE PLD, 5 ns, PQFP44 |

| 封装: | TQFP-44 |

| 文件页数: | 18/48页 |

| 文件大小: | 1136K |

| 代理商: | MACH111SP-5VC |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页当前第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页

MACH 1 & 2 Families

25

MACH111 AND MACH111SP

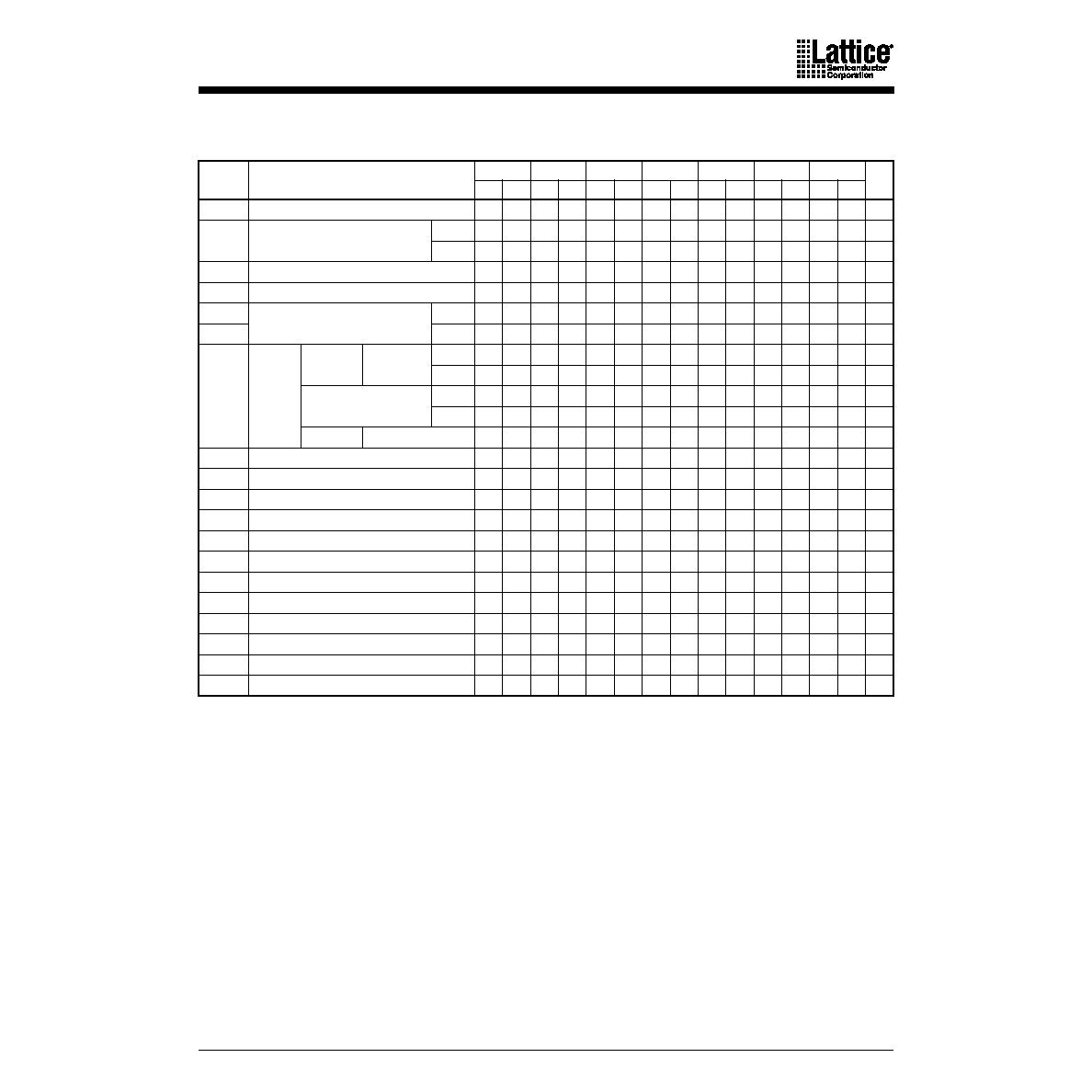

SWITCHING CHARACTERISTICS OVER OPERATING RANGES1

Notes:

1. See “Switching Test Circuit” in the General Information Section of the Vantis 1999 Data Book.

2. These parameters are not 100% tested, but are evaluated at initial characterization and at any time the design is modied where this parameter may be affected.

3. If a signal is powered-down, this parameter must be added to its respective high-speed parameter.

Parameter

Symbol

Parameter Description

-5

-7

-10

-12

-14

-15

-18

Unit

Min Max Min Max Min Max Min Max Min Max Min Max Min Max

tPD

Input, I/O, or Feedback to Combinatorial Output

5

7.5

10

12

14

15

18

ns

tS

Setup Time from Input, I/O, or Feedback

to Clock

D-type

3.5

5.5

6.5

7

8.5

10

12

ns

T-type

4

6.5

7.5

8

10

11

13.5

ns

tH

Register Data Hold Time

0000000

ns

tCO

Clock to Output

3.5

5

6

8

10

12

ns

tWL

Clock Width

LOW

2.5

35666

7.5

ns

tWH

HIGH

2.5

35666

7.5

ns

fMAX

Maximum

Frequency

External

Feedback

1/(tS + tCO)

D-type

143

95

80

66.7

54

50

42

MHz

T-type

133

87

74

62.5

50

47.6

39

MHz

Internal Feedback (fCNT)

D-type

182

133

100

76.9

69

66.6

53

MHz

T-type

167

125

91

71.4

57

55.5

44

MHz

No Feedback 1/(tWL + tWH)

200

167

100

83.3

66.7

MHz

tAR

Asynchronous Reset to Registered Output

7.5

9.5

11

16

19.5

20

24

ns

tARW

Asynchronous Reset Width (Note 2)

4.5

5

7.5

12

14.5

15

18

ns

tARR

Asynchronous Reset Recovery Time (Note 2)

4.5

5

7.5

8

10

12

ns

tAP

Asynchronous Preset to Registered Output

7.5

9.5

11

16

19.5

20

24

ns

tAPW

Asynchronous Preset Width (Note 2)

4.5

5

7.5

12

14.5

15

18

ns

tAPR

Asynchronous Preset Recovery Time (Note 2)

4.5

5

7.5

8

10

12

ns

tEA

Input, I/O, or Feedback to Output Enable

7.5

9.5

10

12

14.5

15

18

ns

tER

Input, I/O, or Feedback to Output Disable

7.5

9.5

10

12

14.5

15

18

ns

tLP

tPD Increase for Powered-down Macrocell (Note 3)

10

ns

tLPS

tS Increase for Powered-down Macrocell (Note 3)

7777777

ns

tLPCO

tCO Increase for Powered-down Macrocell (Note 3)

3333333

ns

tLPEA

tEA Increase for Powered-down Macrocell (Note 3)

10

ns

相关PDF资料 |

PDF描述 |

|---|---|

| MACH111SP-7JC | High-Performance EE CMOS Programmable Logic |

| MACH111SP-7JI | High-Performance EE CMOS Programmable Logic |

| MACH111SP-7VC | High-Performance EE CMOS Programmable Logic |

| MACH131SP-12YI | High-Performance EE CMOS Programmable Logic |

| MACH131SP-14YI | High-Performance EE CMOS Programmable Logic |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MACH111SP-7JC | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH111SP-7JI | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

| MACH111SP-7VC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MACH11SP | 制造商:未知厂家 制造商全称:未知厂家 功能描述:High-Performance EE CMOS In-System Programmable Logic |

| MACH120-12 | 制造商:LATTICE 制造商全称:Lattice Semiconductor 功能描述:High-Performance EE CMOS Programmable Logic |

发布紧急采购,3分钟左右您将得到回复。