- 您现在的位置:买卖IC网 > PDF目录2007 > MAX11040GUU+T (Maxim Integrated Products)IC ADC 24BIT 4CH 38-TSSOP PDF资料下载

参数资料

| 型号: | MAX11040GUU+T |

| 厂商: | Maxim Integrated Products |

| 文件页数: | 25/35页 |

| 文件大小: | 0K |

| 描述: | IC ADC 24BIT 4CH 38-TSSOP |

| 产品培训模块: | Lead (SnPb) Finish for COTS Obsolescence Mitigation Program |

| 标准包装: | 2,500 |

| 位数: | 24 |

| 采样率(每秒): | 64k |

| 数据接口: | DSP,MICROWIRE?,QSPI?,串行,SPI? |

| 转换器数目: | 4 |

| 功率耗散(最大): | 108mW |

| 电压电源: | 模拟和数字 |

| 工作温度: | -40°C ~ 105°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 38-TFSOP(0.173",4.40mm 宽) |

| 供应商设备封装: | 38-TSSOP |

| 包装: | 带卷 (TR) |

| 输入数目和类型: | 4 个差分,双极 |

| 配用: | MAXSPCSPARTAN6+-ND - ADC and DAC Eval Expansion Board |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页当前第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页

MAX11040K/MAX11060

24-/16-Bit, 4-Channel, Simultaneous-Sampling,

Cascadable, Sigma-Delta ADCs

31

Maxim Integrated

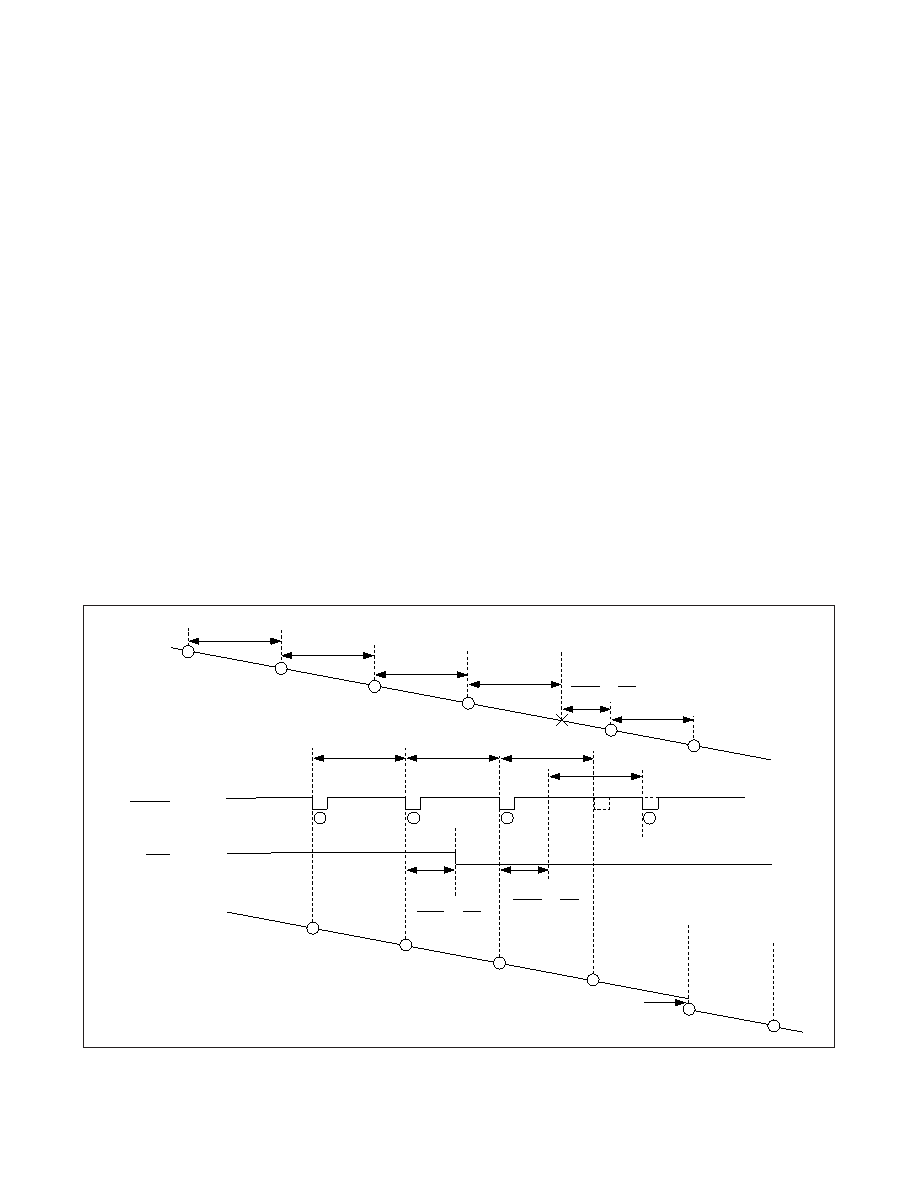

DISCONTINUITY DUE TO SYNC EVENT

DRDYOUT

SYNC

MEASURE

tDRYOUT_TO_SYNC

AIN_

RECONSTRUCTED

DIGITAL OUTPUT

PAUSE FOR

tDRYOUT_TO_SYNC

NOTE: THE LATENCY IS NOT TO SCALE.

tDRYOUT_TO_SYNC

1

2

3

4

2

3

4

5

6

1

2

3

4

5

6

tS

Figure 19. Example of Discontinuity in Reconstructed Digital Output Due to SYNC Falling Edge with a Large DRDYOUT-to-SYNC Delay

Signal Distortion at

SYNC Falling Edges

Each SYNC falling edge causes a disruption in the digi-

tal filter timing proportional to the delay from the previ-

ous falling edge of DRDYOUT to the falling edge of

SYNC. Any analysis of the output data that assumes a

uniform sampling period sees an error proportional to

that delay, with a maximum value determined by the

maximum derivative of the analog input. Figure 19

shows the effect of this discontinuity at output sample 5.

Assuming a 60Hz ±2.2V sine wave, the maximum pos-

sible error on any given sample caused by a SYNC

falling edge is:

VERROR_MAX = 2.2V x 2π x 60Hz x tDRDYOUT_TO_SYNC

= 0.83μV/ns x tDRDYOUT_TO_SYNC

The delay from DRDYOUT to SYNC is quantized to

within one cycle of the 24.576MHz clock. SYNC pulses

that are asynchronous to DRDYOUT may cause large

errors. To eliminate this error, use a single clock source

for all devices and avoid disrupting the output data tim-

ing with SYNC pulses while making high-precision

measurements. Alternately, minimize the delay from

DRDYOUT to SYNC to minimize the error.

Example:

Assume fAIN_ = 60Hz, fS = 16ksps, and eight total

devices in the chain.

Device 1 has the longest tDRDYOUT_TO_SYNC delay,

therefore the worst-case SYNC error.

If device 1 has the fastest XIN clock in the chain, and

device 2 has the slowest XIN clock in the chain, and

they differ by 0.1%, device 1 completes its conversion

as much as 0.1% earlier than device 2. Hence, the

delay of device 2 is:

0.1% x (1/16kHz ) = 62.5ns

The signal then propagates down the chain at a time

delay of nominally 20ns for each device.

The total delay back to the SYNC falling edge after

going through six additional delays is:

tDELAY = 62.5ns + 6 x 20ns = 182.5ns

Maximum % Error = 2

π x fIN x tDRDYOUT_TO_SYNC x

100% = 2 x π x 60Hz x 182.5ns x 100% = 0.007%

The above error is relative to the signal level, not to the

full scale of the data converter.

相关PDF资料 |

PDF描述 |

|---|---|

| MAX11046ECB+T | IC ADC 16BIT PAR 250KSPS 64TQFP |

| MAX11046ETN+T | ADC 16BIT SAMPLING 8CH 56-TQFN |

| MAX11049ECB+ | IC ADC 16BIT PAR 250KSPS 64TQFP |

| MAX1104EUA+ | IC CODEC 8BIT 8-UMAX |

| MAX11100EUB+ | IC ADC 16BIT SRL 200KSPS 10UMAX |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MAX11040K | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:24-/16-Bit, 4-Channel, Simultaneous-Sampling, Cascadable, Sigma-Delta ADCs |

| MAX11040K_1111 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:24-/16-Bit, 4-Channel, Simultaneous-Sampling, Cascadable, Sigma-Delta ADCs |

| MAX11040K_12 | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:MAX11040K Evaluation Kit/Daughterboard |

| MAX11040KDBEVKIT | 制造商:MAXIM 制造商全称:Maxim Integrated Products 功能描述:MAX11040K Evaluation Kit/Daughterboard |

| MAX11040KDBEVKIT# | 功能描述:数据转换 IC 开发工具 MAX5135/11040/11612 Eval Kit w/ FMC RoHS:否 制造商:Texas Instruments 产品:Demonstration Kits 类型:ADC 工具用于评估:ADS130E08 接口类型:SPI 工作电源电压:- 6 V to + 6 V |

发布紧急采购,3分钟左右您将得到回复。