- 您现在的位置:买卖IC网 > PDF目录69024 > MC13224V (FREESCALE SEMICONDUCTOR INC) SPECIALTY MICROPROCESSOR CIRCUIT, PBGA99 PDF资料下载

参数资料

| 型号: | MC13224V |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PBGA99 |

| 封装: | 9.50 X 9.50 MM, 1.20 MM HEIGHT, ROHS COMPLIANT, LGA-99 |

| 文件页数: | 41/54页 |

| 文件大小: | 490K |

| 代理商: | MC13224V |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页当前第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页

MC1322x Technical Data, Rev. 1.3

46

Freescale Semiconductor

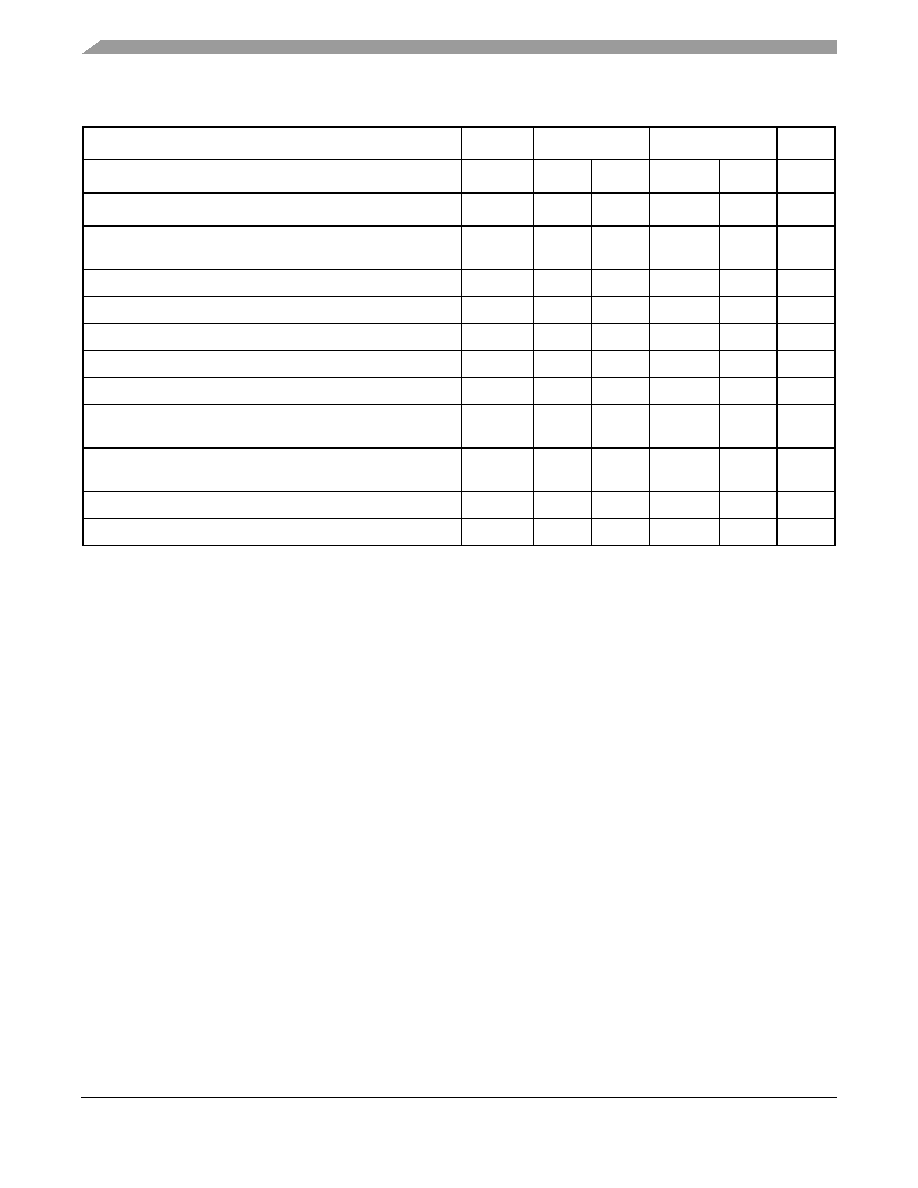

Table 20. I2C Signal AC Specifications1

1 All values referred to V

IHmin and VILmax levels

Parameter

Symbol

Standard-Mode

Fast-Mode

Unit

Min

Max

Min

Max

SCL clock frequency (when source)

fSCL

0

100

0

150

kHz

Hold time (repeated) START condition.

After this period, the first clock pulse is generated

tHD;STA

4.0

-

0.6

-

μs

LOW period of the SCL clock

tLOW

4.7

-

1.3

-

μs

HIGH period of the SCL clock

tHIGH

4.0

-

0.6

-

μs

Set-up time for a repeated START condition

tSU;STA

4.7

-

0.6

-

μs

Data hold time

tSHD;DAT

02

2 A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the V

IHmin of the SCL

signal) to bridge the undefined region of the falling edge of SCL.

3.453

3 The maximum t

HD;DAT has only to be met if the device does not stretch the LOW period (tLOW) of the SCL signal.

μs

Data setup time

tSU:DAT

250

-

1004

4 A Fast-mode I2C-bus device can be used in a Standard-mode I2C-bus system, but the requirement t

SU;DAT >= 250 ns

must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal.

If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line tr max

+ tSU;DAT = 1000 + 250 = 1250 ns (according to the Standard-mode I2C-bus specification) before the SCL line is

released.

-ns

Rise time for both SDA and SCL signals

tr

-

1000

20 +

0.1Cb

5

5 C

b = total capacitance of one bus line in pF. If mixed with Hs-mode devices, the faster fall-times are allowed.

300

ns

Fall time for both SDA and SCL signals

tf

-

300

20 +

0.1Cb

300

ns

Bus free time between a STOP and START condition

tBUF

4.7

-

1.3

-

μs

Capacitive load for each bus line

Cb

-

400

-

400

pF

相关PDF资料 |

PDF描述 |

|---|---|

| MC141556P1 | UNIVERSAL SERIAL BUS CONTROLLER, PDIP28 |

| MC141556P1 | UNIVERSAL SERIAL BUS CONTROLLER, PDIP28 |

| MC14536BFL2 | 1 TIMER(S), PROGRAMMABLE TIMER, PDSO16 |

| MC14536BFL1 | 1 TIMER(S), PROGRAMMABLE TIMER, PDSO16 |

| MC146805E2CL | 8-BIT, MICROCONTROLLER, CDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC13224V | 制造商:Freescale Semiconductor 功能描述:; Controller Family/Series:(ARM7); Memor |

| MC13224V_09 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Advanced ZigBee?- Compliant Platform-in-Package (PiP) for the 2.4 GHz IEEE? 802.15.4 Standard |

| MC13224VR2 | 功能描述:射频收发器 PIP 802.15.4 2.4G IND RoHS:否 制造商:Atmel 频率范围:2322 MHz to 2527 MHz 最大数据速率:2000 Kbps 调制格式:OQPSK 输出功率:4 dBm 类型: 工作电源电压:1.8 V to 3.6 V 最大工作温度:+ 85 C 接口类型:SPI 封装 / 箱体:QFN-32 封装:Tray |

| MC13224VR2 | 制造商:Freescale Semiconductor 功能描述:IC 32BIT MCU ARM7 26MHZ LGA-99 |

| MC13224VR2-CUT TAPE | 制造商:Freescale 功能描述:MC13224 Series 2.4 GHz PIP 250 KBps Surface Mount RF Transceiver - LGA-99 |

发布紧急采购,3分钟左右您将得到回复。