- 您现在的位置:买卖IC网 > PDF目录67964 > MC56F8357VPY60 (FREESCALE SEMICONDUCTOR INC) 16-BIT, 120 MHz, OTHER DSP, PQFP160 PDF资料下载

参数资料

| 型号: | MC56F8357VPY60 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 16-BIT, 120 MHz, OTHER DSP, PQFP160 |

| 封装: | PLASTIC, LQFP-160 |

| 文件页数: | 10/177页 |

| 文件大小: | 4091K |

| 代理商: | MC56F8357VPY60 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页

Operating Modes

56F8357 Technical Data, Rev. 15

Freescale Semiconductor

107

Preliminary

6.3 Operating Modes

Since the SIM is responsible for distributing clocks and resets across the chip, it must understand the

various chip operating modes and take appropriate action. These are:

Reset Mode, which has two submodes:

— POR and RESET operation

The 56800E core and all peripherals are reset. This occurs when the internal POR is asserted or the

RESET pin is asserted.

— COP reset and software reset operation

The 56800E core and all peripherals are reset. The MA bit within the OMR is not changed. This allows

the software to determine the boot mode (internal or external boot) to be used on the next reset.

Run Mode

This is the primary mode of operation for this device. In this mode, the 56800E controls chip operation

Debug Mode

The 56800E is controlled via JTAG/EOnCE when in debug mode. All peripherals, except the COP and

PWMs, continue to run. COP is disabled and PWM outputs are optionally switched off to disable any motor

from being driven; see the PWM chapter in the 56F8300 Peripheral User Manual for details.

Wait Mode

In Wait mode, the core clock and memory clocks are disabled. Optionally, the COP can be stopped.

Similarly, it is an option to switch off PWM outputs to disable any motor from being driven. All other

peripherals continue to run.

Stop Mode

When in Stop mode, the 56800E core, memory, and most peripheral clocks are shut down. Optionally, the

COP and CAN can be stopped. For lowest power consumption in Stop mode, the PLL can be shut down.

This must be done explicitly before entering Stop mode, since there is no automatic mechanism for this. The

CAN (along with any non-gated interrupt) is capable of waking the chip up from Stop mode, but is not fully

functional in Stop mode.

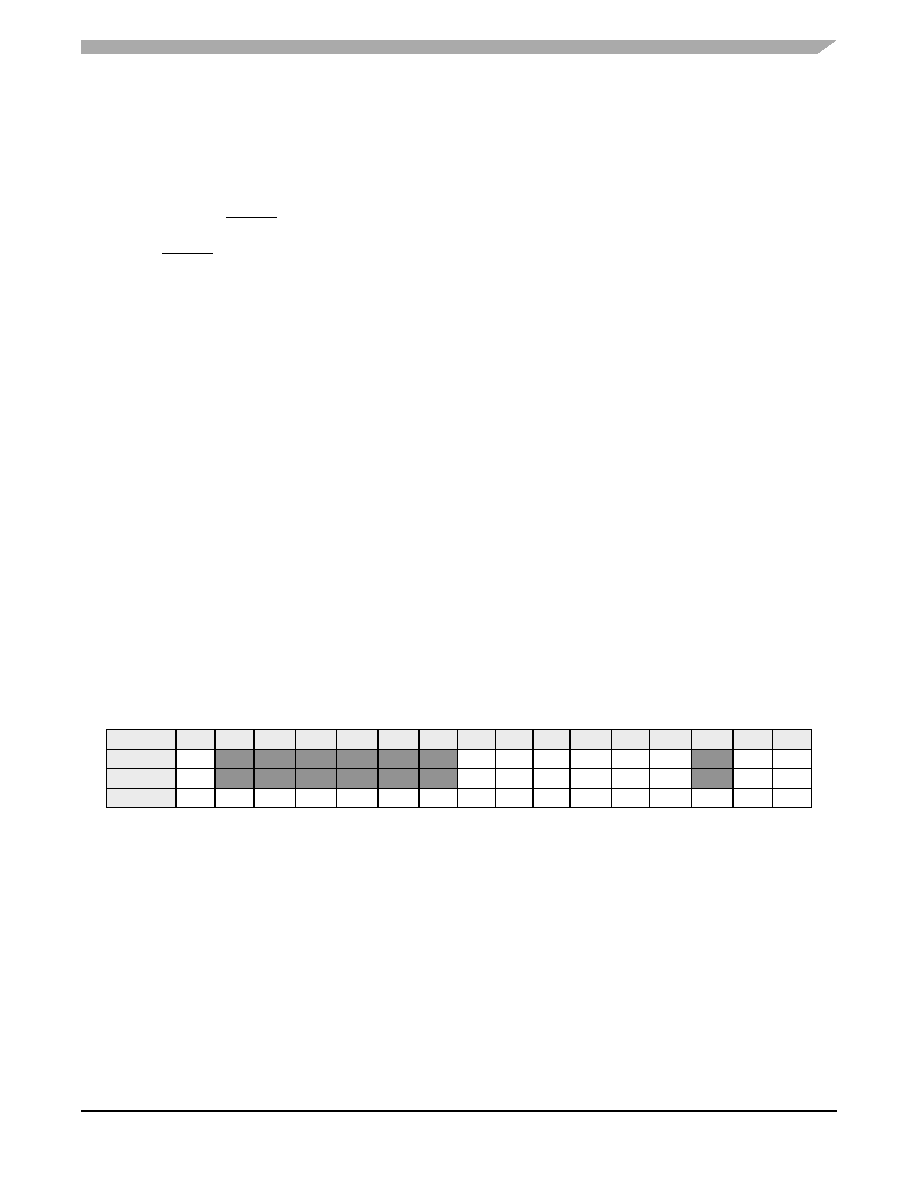

6.4 Operating Mode Register

Figure 6-1 OMR

The reset state for MB and MA will depend on the Flash secured state. See Part 4.2 and Part 7 for detailed

information on how the Operating Mode Register (OMR) MA and MB bits operate in this device. For all

other bits, see the DSP56800E Reference Manual.

Note:

The OMR is not a Memory Map register; it is directly accessible in code through the acronym OMR.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

NL

CM

XP

SD

R

SA

EX

0

MB

MA

Type

R/W

RESET

0

0000

0

X

Because

of

an

order

from

the

United

States

International

Trade

Commission,

BGA-packaged

product

lines

and

part

numbers

indicated

here

currently

are

not

available

from

Freescale

for

import

or

sale

in

the

United

States

prior

to

September

2010:

MC56F8357,

MC56F8157

相关PDF资料 |

PDF描述 |

|---|---|

| MC56F8166VFV | 16-BIT, 120 MHz, OTHER DSP, PQFP144 |

| MC56F8366MFVE | 16-BIT, 120 MHz, OTHER DSP, PQFP144 |

| MC56F8366VFVE | 16-BIT, 120 MHz, OTHER DSP, PQFP144 |

| MC56F8366VFV60 | 16-BIT, 120 MHz, OTHER DSP, PQFP144 |

| MC56F8335MFGE | 4-BIT, 120 MHz, OTHER DSP, PQFP128 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC56F8357VPYE | 功能描述:数字信号处理器和控制器 - DSP, DSC 16 BIT HYBRID CNTRLR RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MC56F8357VVF | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| MC56F8357VVFE | 功能描述:数字信号处理器和控制器 - DSP, DSC 16 BIT HYBRID CNTRLR RoHS:否 制造商:Microchip Technology 核心:dsPIC 数据总线宽度:16 bit 程序存储器大小:16 KB 数据 RAM 大小:2 KB 最大时钟频率:40 MHz 可编程输入/输出端数量:35 定时器数量:3 设备每秒兆指令数:50 MIPs 工作电源电压:3.3 V 最大工作温度:+ 85 C 封装 / 箱体:TQFP-44 安装风格:SMD/SMT |

| MC56F8357VVFEJ | 制造商:Freescale Semiconductor 功能描述:16 BIT HYBRID CONTROLLER - Bulk |

| MC56F8365 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

发布紧急采购,3分钟左右您将得到回复。