- 您现在的位置:买卖IC网 > PDF目录67964 > MC56F8366VFVE (FREESCALE SEMICONDUCTOR INC) 16-BIT, 120 MHz, OTHER DSP, PQFP144 PDF资料下载

参数资料

| 型号: | MC56F8366VFVE |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 数字信号处理 |

| 英文描述: | 16-BIT, 120 MHz, OTHER DSP, PQFP144 |

| 封装: | ROHS COMPLIANT, LQFP-144 |

| 文件页数: | 103/182页 |

| 文件大小: | 1149K |

| 代理商: | MC56F8366VFVE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页当前第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页

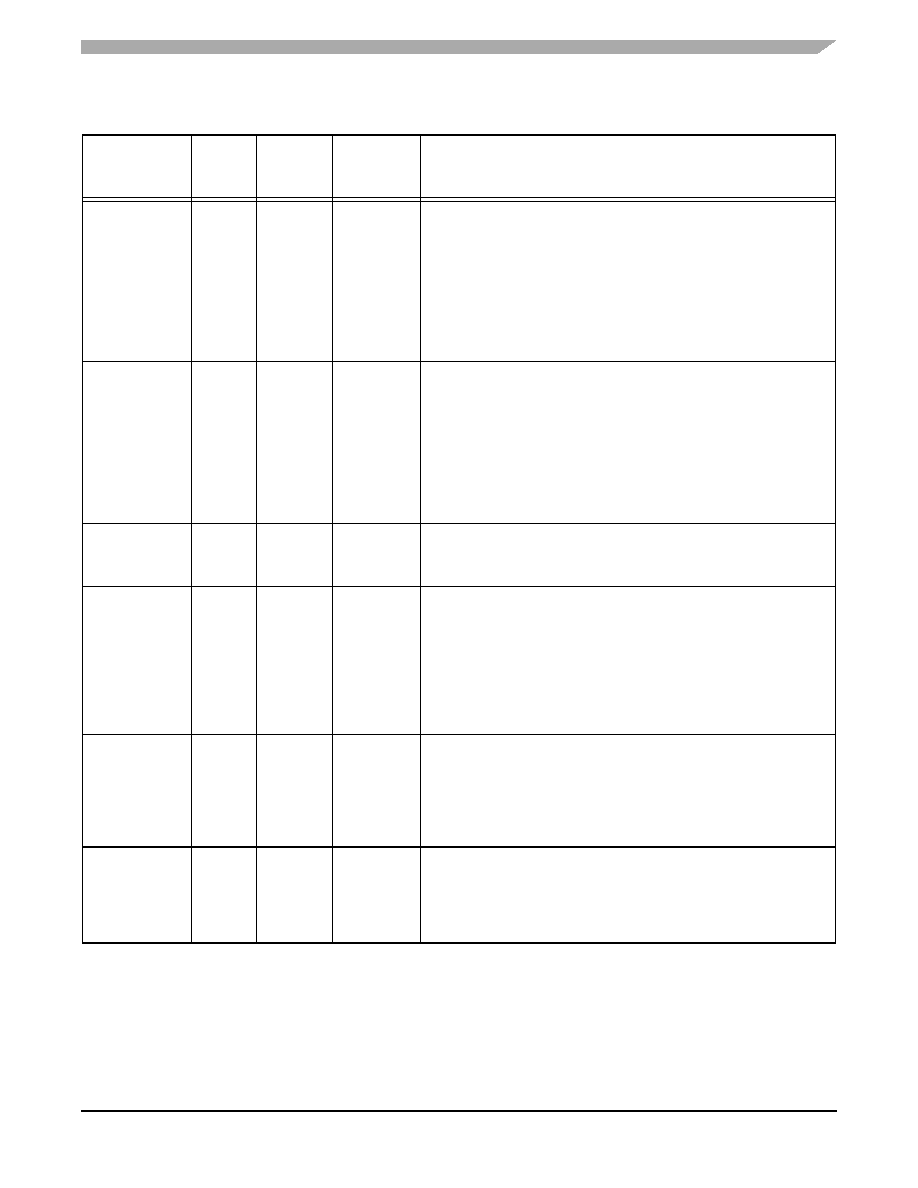

Signal Pins

56F8366 Technical Data, Rev. 7

Freescale Semiconductor

27

Preliminary

TXD1

(GPIOD6)

42

Output

Input/

Output

In reset,

output is

disabled,

pull-up is

enabled

Transmit Data — SCI1 transmit data output

Port D GPIO — This GPIO pin can be individually programmed as

an input or output pin.

After reset, the default state is SCI output.

To deactivate the internal pull-up resistor, clear bit 6 in the

GPIOD_PUR register.

RXD1

(GPIOD7)

43

Input

Input/

Output

Input,

pull-up

enabled

Receive Data — SCI1 receive data input

Port D GPIO — This GPIO pin can be individually programmed as

an input or output pin.

After reset, the default state is SCI input.

To deactivate the internal pull-up resistor, clear bit 7 in the

GPIOD_PUR register.

TCK

121

Schmitt

Input

Input,

pulled low

internally

Test Clock Input — This input pin provides a gated clock to

synchronize the test logic and shift serial data to the JTAG/EOnCE

port. The pin is connected internally to a pull-down resistor.

TMS

122

Schmitt

Input

Input,

pulled high

internally

Test Mode Select Input — This input pin is used to sequence the

JTAG TAP controller’s state machine. It is sampled on the rising

edge of TCK and has an on-chip pull-up resistor.

To deactivate the internal pull-up resistor, set the JTAG bit in the

SIM_PUDR register.

Note:

Always tie the TMS pin to VDD through a 2.2K resistor.

TDI

123

Schmitt

Input

Input,

pulled high

internally

Test Data Input — This input pin provides a serial input data

stream to the JTAG/EOnCE port. It is sampled on the rising edge

of TCK and has an on-chip pull-up resistor.

To deactivate the internal pull-up resistor, set the JTAG bit in the

SIM_PUDR register.

TDO

124

Output

In reset,

output is

disabled,

pull-up is

enabled

Test Data Output — This tri-stateable output pin provides a serial

output data stream from the JTAG/EOnCE port. It is driven in the

shift-IR and shift-DR controller states, and changes on the falling

edge of TCK.

Table 2-2 Signal and Package Information for the 144-Pin LQFP

Signal Name

Pin No.

Type

State

During

Reset

Signal Description

相关PDF资料 |

PDF描述 |

|---|---|

| MC56F8366VFV60 | 16-BIT, 120 MHz, OTHER DSP, PQFP144 |

| MC56F8335MFGE | 4-BIT, 120 MHz, OTHER DSP, PQFP128 |

| MC68008LC8 | 16-BIT, 8 MHz, MICROPROCESSOR, CDIP48 |

| MC68008L8 | 16-BIT, 8 MHz, MICROPROCESSOR, CDIP48 |

| MC68008CLC8 | 16-BIT, 8 MHz, MICROPROCESSOR, CDIP48 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC56F8367 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| MC56F8367E | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:16-bit Digital Signal Controllers |

| MC56F8367EVM | 功能描述:开发板和工具包 - 其他处理器 MC56F8367 EVAL BOARD RoHS:否 制造商:Freescale Semiconductor 产品:Development Systems 工具用于评估:P3041 核心:e500mc 接口类型:I2C, SPI, USB 工作电源电压: |

| MC56F8367EVME | 功能描述:开发板和工具包 - 其他处理器 MC56F8367 EVALUATION BOARD RoHS:否 制造商:Freescale Semiconductor 产品:Development Systems 工具用于评估:P3041 核心:e500mc 接口类型:I2C, SPI, USB 工作电源电压: |

| MC56F8367EVME | 制造商:Freescale Semiconductor 功能描述:MC56F8367 EVALUATION BOA |

发布紧急采购,3分钟左右您将得到回复。