- 您现在的位置:买卖IC网 > PDF目录80445 > MC68HC05C8AMFB (FREESCALE SEMICONDUCTOR INC) 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | MC68HC05C8AMFB |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 2.1 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | QFP-44 |

| 文件页数: | 58/116页 |

| 文件大小: | 781K |

| 代理商: | MC68HC05C8AMFB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页当前第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页

Timer

MC68HC05C8A MC68HCL05C8A MC68HSC05C8A Data Sheet, Rev. 5.1

46

Freescale Semiconductor

8.6 Timer Status Register

The timer status register (TSR) is a read-only register containing three status flag bits.

ICF — Input Capture Flag

1 = Flag set when selected polarity edge is sensed by input capture edge detector

0 = Flag cleared when TSR and input capture low register ($15) are accessed

OCF — Output Compare Flag

1 = Flag set when output compare register contents match the free-running counter contents

0 = Flag cleared when TSR and output compare low register ($17) are accessed

TOF — Timer Overflow Flag

1 = Flag set when free-running counter transition from $FFFF to $0000 occurs

0 = Flag cleared when TSR and counter low register ($19) are accessed

Bits 0–4 — Not used

Always read 0

Accessing the timer status register satisfies the first condition required to clear status bits. The remaining

step is to access the register corresponding to the status bit.

A problem can occur when using the timer overflow function and reading the free-running counter at

random times to measure an elapsed time. Without incorporating the proper precautions into software,

the timer overflow flag could unintentionally be cleared if:

1.

The timer status register is read or written when TOF is set.

2.

The LSB of the free-running counter is read but not for the purpose of servicing the flag.

The counter alternate register at addresses $1A and $1B contains the same value as the free-running

counter (at address $18 and $19); therefore, this alternate register can be read at any time without

affecting the timer overflow flag in the timer status register.

8.7 Timer During Wait Mode

The central processor unit (CPU) clock halts during wait mode, the timer remains active. If interrupts are

enabled, a timer interrupt will cause the processor to exit the wait mode.

8.8 Timer During Stop Mode

In stop mode, the timer stops counting and holds the last count value if stop is exited by an interrupt. If

reset is used, the counter is forced to $FFFC. During stop, if at least one valid input capture edge occurs

at the TCAP pin, the input capture detect circuit is armed. This does not set any timer flags or wake up

the microcontroller unit (MCU). But if the MCU exits stop due to an external interrupt, there is an active

input capture flag and data from the first valid edge that occurred during the stop mode. If reset is used

to exit stop mode, then no input capture flag or data remains, even if a valid input capture edge occurred.

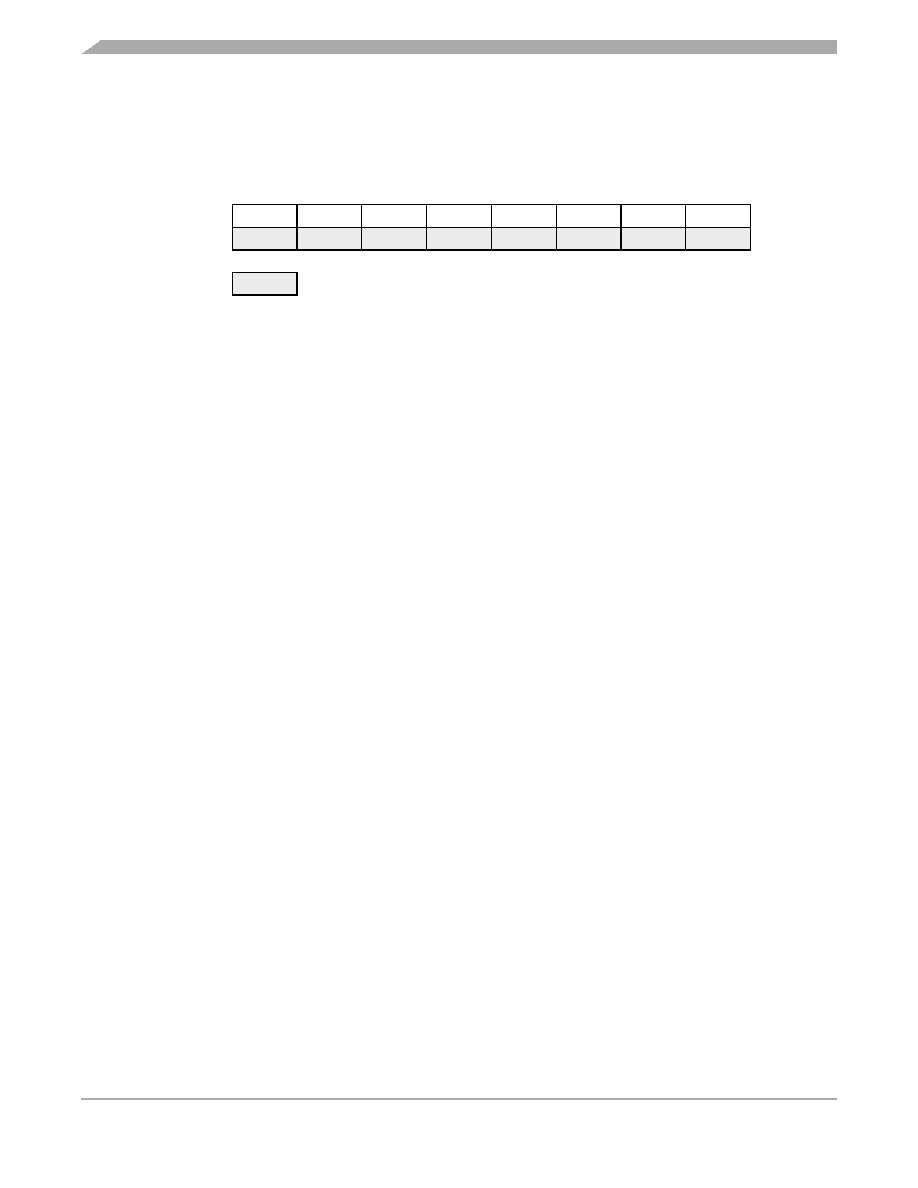

Address:

$0013

Bit 7

654321

Bit 0

Read:

ICF

OCF

TOF

00000

Write:

Reset:

U

00000

= Unimplemented

U = Unaffected

Figure 8-4. Timer Status Register (TSR)

相关PDF资料 |

PDF描述 |

|---|---|

| MPC8250ACVRMIBX | 32-BIT, 266 MHz, RISC PROCESSOR, PBGA516 |

| MPC860TZQ50D4R2 | 32-BIT, 50 MHz, RISC PROCESSOR, PBGA357 |

| MC908GZ48VFU | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP64 |

| MC9S12GC32PCFA25 | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP48 |

| MC9S12KG128CPU | 16-BIT, FLASH, 25 MHz, MICROCONTROLLER, PQFP100 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC68HC05C9 | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:TECHNICAL DATA |

| MC68HC05C9A | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC68HC05C9AB | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC68HC05C9AFB | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

| MC68HC05C9AFN | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Microcontrollers |

发布紧急采购,3分钟左右您将得到回复。