- 您现在的位置:买卖IC网 > PDF目录45277 > MC8640DTHX1250HE (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 PDF资料下载

参数资料

| 型号: | MC8640DTHX1250HE |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 |

| 封装: | 33 X 33 MM, CERAMIC, FCBGA-1023 |

| 文件页数: | 52/130页 |

| 文件大小: | 1495K |

| 代理商: | MC8640DTHX1250HE |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页当前第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页

MPC8640 and MPC8640D Integrated Host Processor Hardware Specifications, Rev. 3

28

Freescale Semiconductor

Ethernet: Enhanced Three-Speed Ethernet (eTSEC), MII Management

clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out

onto the TSECn_GTX_CLK pin (while transmit data appears on TSECn_TXD[7:0], for example). It is

intended that external receivers capture eTSEC transmit data using the clock on TSECn_GTX_CLK as a

source- synchronous timing reference. Typically, the clock edge that launched the data can be used, since

the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is

relationship between the maximum FIFO speed and the platform speed. For more information, see

NOTE

The phase between the output clocks TSEC1_GTX_CLK and

TSEC2_GTX_CLK (ports 1 and 2) is no more than 100 ps. The phase

between the output clocks TSEC3_GTX_CLK and TSEC4_GTX_CLK

(ports 3 and 4) is no more than 100 ps.

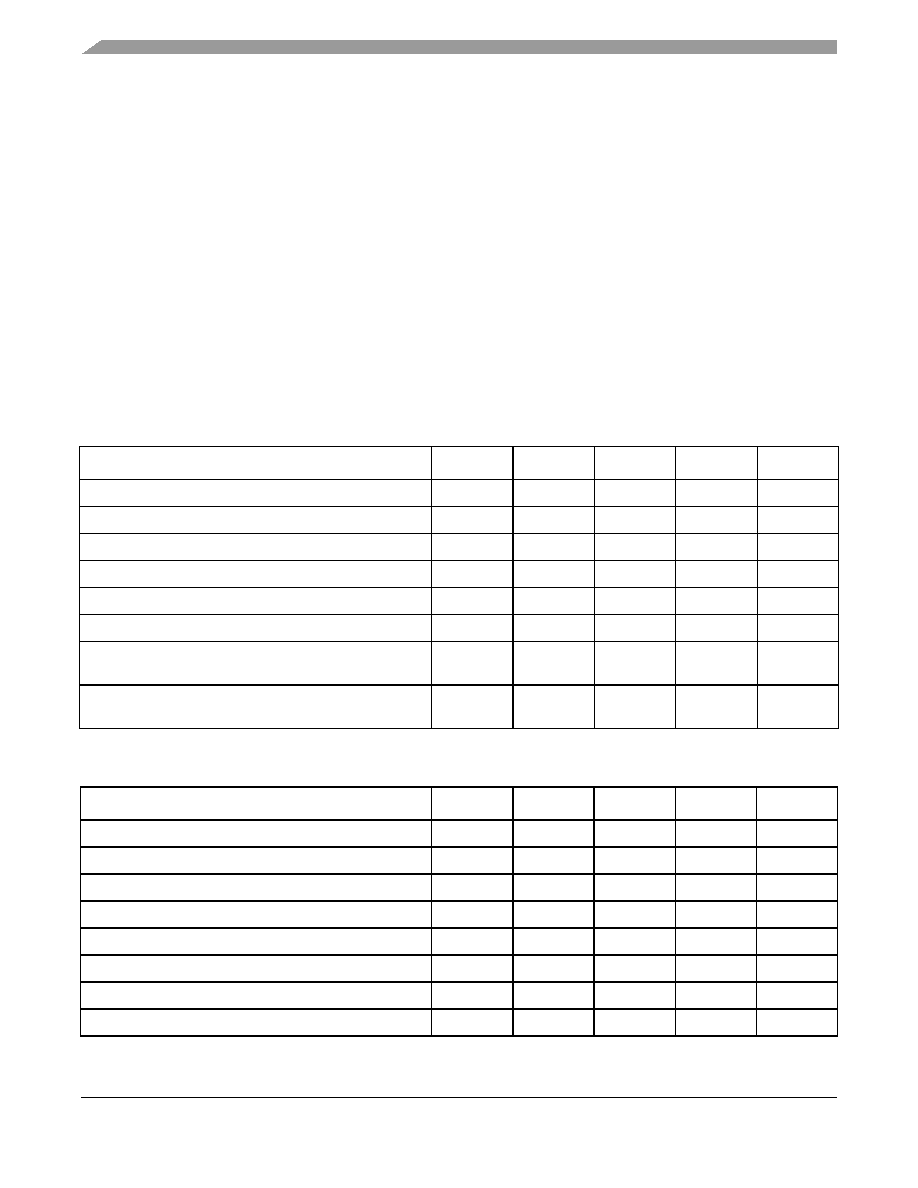

Table 26. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with L/TVDD of 3.3 V ± 5% and 2.5 V ± 5%.

Parameter

Symbol

Min

Typ

Max

Unit

TX_CLK, GTX_CLK clock period (GMII mode)

tFIT

8.4

8.0

100

ns

TX_CLK, GTX_CLK clock period (Encoded mode)

tFIT

6.4

8.0

100

ns

TX_CLK, GTX_CLK duty cycle

tFITH/tFIT

45

50

55

%

TX_CLK, GTX_CLK peak-to-peak jitter

tFITJ

—

250

ps

Rise time TX_CLK (20%–80%)

tFITR

—

0.75

ns

Fall time TX_CLK (80%–20%)

tFITF

—

0.75

ns

FIFO data TXD[7:0], TX_ER, TX_EN setup time to

GTX_CLK

tFITDV

2.0

—

ns

GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold

time

tFITDX

0.5

—

3.0

ns

Table 27. FIFO Mode Receive AC Timing Specification

At recommended operating conditions with L/TVDD of 3.3 V ± 5% and 2.5 V ± 5%.

Parameter

Symbol

Min

Typ

Max

Unit

RX_CLK clock period (GMII mode)

tFIR

1

8.4

8.0

100

ns

RX_CLK clock period (Encoded mode)

tFIR

6.4

8.0

100

ns

RX_CLK duty cycle

tFIRH/tFIR

45

50

55

%

RX_CLK peak-to-peak jitter

tFIRJ

—

250

ps

Rise time RX_CLK (20%–80%)

tFIRR

—

0.75

ns

Fall time RX_CLK (80%–20%)

tFIRF

—

0.75

ns

RXD[7:0], RX_DV, RX_ER setup time to RX_CLK

tFIRDV

1.5

—

ns

RXD[7:0], RX_DV, RX_ER hold time to RX_CLK

tFIRDX

0.5

—

ns

相关PDF资料 |

PDF描述 |

|---|---|

| MC8640VU1250HE | 32-BIT, 1250 MHz, MICROPROCESSOR, CBGA1023 |

| MC8640THX1000HC | 32-BIT, 1000 MHz, MICROPROCESSOR, CBGA1023 |

| MC8640TVU1067NC | 32-BIT, 1067 MHz, MICROPROCESSOR, CBGA1023 |

| MC8641DHX1250NB | MICROPROCESSOR, CBGA1023 |

| MC8641DHX1500NB | MICROPROCESSOR, CBGA1023 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC8640DTHX1250N | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications |

| MC8640DTVJ1067NE | 功能描述:IC MPU E600 DUAL CORE 1023FCCBGA 制造商:nxp usa inc. 系列:MPC86xx 包装:托盘 零件状态:在售 核心处理器:PowerPC e600 核数/总线宽度:2 ??,32 位 速度:1.067GHz 协处理器/DSP:- RAM 控制器:DDR,DDR2 图形加速:无 显示与接口控制器:- 以太网:10/100/1000 Mbps(4) SATA:- USB:- 电压 - I/O:1.8V,2.5V,3.3V 工作温度:-40°C ~ 105°C(TA) 安全特性:- 封装/外壳:1023-BCBGA,FCCBGA 供应商器件封装:1023-FCCBGA(33x33) 附加接口:DUART,HSSI,I2C,RapidIO 标准包装:24 |

| MC8640DTVU1000H | 制造商:FREESCALE 制造商全称:Freescale Semiconductor, Inc 功能描述:Integrated Host Processor Hardware Specifications Addendum for the MC8640xTxxyyyyaC Series |

| MC8640DTVU1000HC | 功能描述:微处理器 - MPU G8 REV2.1 1.05V -40/105C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MC8640DTVU1000HE | 功能描述:微处理器 - MPU G8 REV3.0 0.95V 105C RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

发布紧急采购,3分钟左右您将得到回复。