- 您现在的位置:买卖IC网 > PDF目录26811 > MC88LV926DW (INTEGRATED DEVICE TECHNOLOGY INC) 88LV SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO20 PDF资料下载

参数资料

| 型号: | MC88LV926DW |

| 厂商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分类: | 时钟及定时 |

| 英文描述: | 88LV SERIES, PLL BASED CLOCK DRIVER, 4 TRUE OUTPUT(S), 1 INVERTED OUTPUT(S), PDSO20 |

| 封装: | PLASTIC, SOIC-20 |

| 文件页数: | 4/11页 |

| 文件大小: | 285K |

| 代理商: | MC88LV926DW |

Advanced Clock Drivers Device Data

2

Freescale Semiconductor

MC88LV926

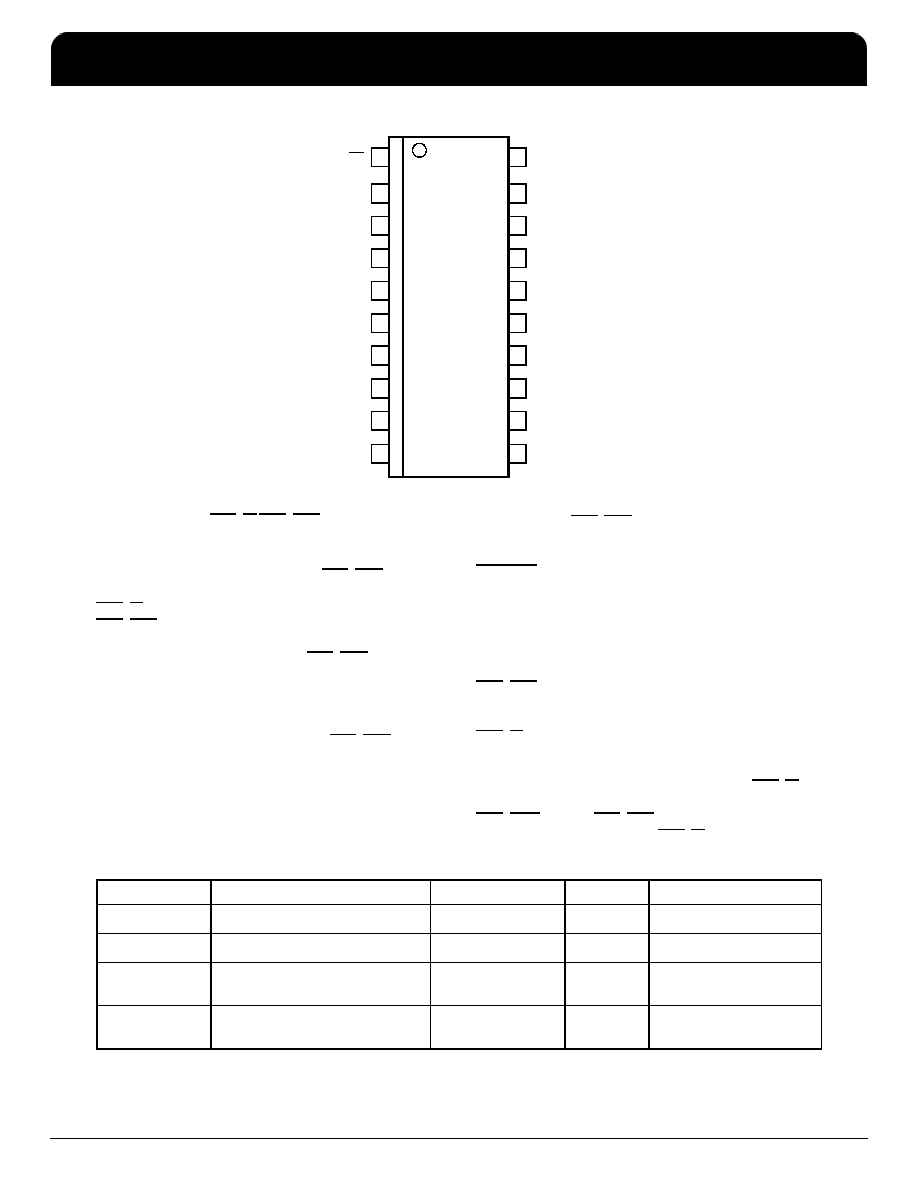

Figure 1. Pinout: 20-Lead Wide SOIC Package (Top View)

Description of the RST_IN/RST_OUT(LOCK)

Functionality (continued)

After the system start-up is complete and the 88LV926 is

phase-locked to the SYNC input signal (RST_OUT high), the

processor reset functionality can be utilized. When the

RST_IN pin is toggled low (min. pulse width=10 nS),

RST_OUT(LOCK) will go to the low state and remain there

for 1024 cycles of the ‘Q' output frequency (512 SYNC

cycles). During the time in which the RST_OUT(LOCK) is

actively pulled low, all the 88LV926 clock outputs will continue

operating correctly and in a locked condition to the SYNC

input (clock signals to the 68030/040/060 family of

processors must continue while the processor is in reset). A

propagation delay after the 1024th cycle RST_OUT(LOCK)

goes back to the high impedance state to be pulled high by

the resistor.

Power Supply Ramp Rate Restriction for Correct 030/040

Processor Reset Operation During System Start-up

Because the RST_OUT(LOCK) pin is an indicator of

phase-lock to the reference source, some constraints must

be placed on the power supply ramp rate to make sure the

RST_OUT(LOCK) signal holds the processor in reset during

system start-up (power-up). With the recommended loop filter

values (see Figure 7) the lock time is approximately 10ms.

The phase-lock loop will begin attempting to lock to a

reference source (if it is present) when VCC reaches 2 V. If the

VCC ramp rate is significantly slower than 10 ms, then the

PLL could lock to the reference source, causing

RST_OUT(LOCK) to go high before the 88LV926 and 030/

040 processor is fully powered up, violating the processor

reset specification. Therefore, if it is necessary for the

RST_IN pin to be held high during power-up, the VCC ramp

rate must be less than 10 mS for proper 68030/040/060 reset

operation.

This ramp rate restriction can be ignored if the RST_IN pin

can be held low during system start-up (which holds

RST_OUT low). The RST_OUT(LOCK) pin will then be pulled

back high 1024 cycles after the RST_IN pin goes high.

19

20

18

17

16

15

14

13

12

11

2

1

3

4

5

6

7

8

9

10

GND

Q3

2X_Q

VCC

QCLKEN

MR

VCC

RST_IN

Q2

VCC(AN)

GND

RC1

RST_OUT(LOCK)

GND(AN)

PLL_EN

SYNC

Q1

GND

VCC

Q0

Table 1. Capacitance and Power Specifications

Symbol

Parameter

Value Type

Unit

Test Conditions

CIN

Input Capacitance

4.5(1)

1. Value at VCC = 3.3 V TBD

pF

VCC = 3.3 V

CPD

Power Dissipation Capacitance

40(1)

pF

VCC = 3.3 V

PD1

Power Dissipation at 33MHz With 50

Ω

Thevenin Termination

15mW/Output(1)

90mW/Device

mW

VCC = 3.3 V

T = 25

°C

PD2

Power Dissipation at 33MHz With 50

Ω

Parallel Termination to GND

37.5mW/Output(1)

225mW/Device

mW

VCC = 3.3 V

T = 25

°C

MC88LV926

Low Skew CMOS PLL 68060 Clock Driver

NETCOM

IDT Low Skew CMOS PLL 68060 Clock Driver

Freescale Timing Solutions Organization has been acquired by Integrated Device Technology, Inc

MC88LV926

2

相关PDF资料 |

PDF描述 |

|---|---|

| MD2FLDL-TTL-35G | ACTIVE DELAY LINE, TRUE OUTPUT, DSO6 |

| MD2FLDL-TTL-7F | ACTIVE DELAY LINE, TRUE OUTPUT, DIP6 |

| MD2FLDL-TTL-80G | ACTIVE DELAY LINE, TRUE OUTPUT, DSO6 |

| MD2FLDL-TTL-200G | ACTIVE DELAY LINE, TRUE OUTPUT, DSO6 |

| MD2FLDL-TTL-150T | ACTIVE DELAY LINE, TRUE OUTPUT, DSO6 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC88LV926DWR2 | 功能描述:IC DRIVER CLK PLL 66MHZ 20-SOIC RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MC88LV926EG | 功能描述:IC PLL CLOCK DRIVER 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MC88LV926EGR2 | 功能描述:IC PLL CLOCK DRIVER 20-SOIC RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT |

| MC88PL117 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:CMOS PLL CLOCK DRIVER |

| MC88PL117FN | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:CMOS PLL CLOCK DRIVER |

发布紧急采购,3分钟左右您将得到回复。