- 您现在的位置:买卖IC网 > PDF目录69030 > MC9328MXSCVF10 (FREESCALE SEMICONDUCTOR INC) 32-BIT, 100 MHz, MICROPROCESSOR, PBGA225 PDF资料下载

参数资料

| 型号: | MC9328MXSCVF10 |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 100 MHz, MICROPROCESSOR, PBGA225 |

| 封装: | 13 X 13 MM, PLASTIC, BGA-225 |

| 文件页数: | 45/72页 |

| 文件大小: | 1411K |

| 代理商: | MC9328MXSCVF10 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页当前第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页

Signals and Connections

MC9328MXS Advance Information, Rev. 0

Freescale Semiconductor

5

2 Signals and Connections

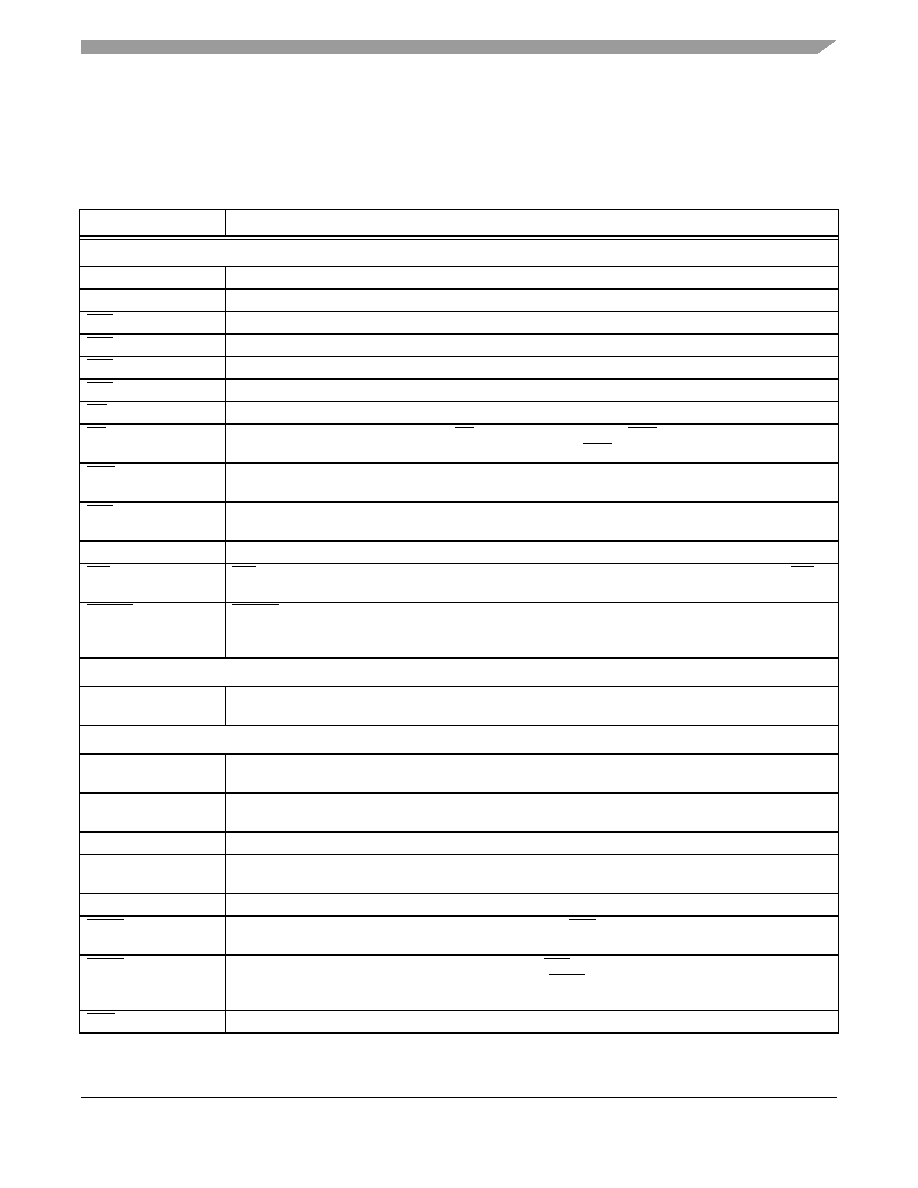

Table 3 identifies and describes the i.MX processor signals that are assigned to package pins. The signals are

grouped by the internal module that they are connected to.

Table 3. MC9328MXS Signal Descriptions

Signal Name

Function/Notes

External Bus/Chip-Select (EIM)

A[24:0]

Address bus signals

D[31:0]

Data bus signals

EB0

MSB Byte Strobe—Active low external enable byte signal that controls D [31:24].

EB1

Byte Strobe—Active low external enable byte signal that controls D [23:16].

EB2

Byte Strobe—Active low external enable byte signal that controls D [15:8].

EB3

LSB Byte Strobe—Active low external enable byte signal that controls D [7:0].

OE

Memory Output Enable—Active low output enables external data bus.

CS [5:0]

Chip-Select—The chip-select signals CS [3:2] are multiplexed with CSD [1:0] and are selected by the

Function Multiplexing Control Register (FMCR). By default CSD [1:0] is selected.

ECB

Active low input signal sent by a flash device to the EIM whenever the flash device must terminate an

on-going burst sequence and initiate a new (long first access) burst sequence.

LBA

Active low signal sent by a flash device causing the external burst device to latch the starting burst

address.

BCLK (burst clock)

Clock signal sent to external synchronous memories (such as burst flash) during burst mode.

RW

RW signal—Indicates whether external access is a read (high) or write (low) cycle. Used as a WE

input signal by external DRAM.

DTACK

DTACK signal—The external input data acknowledge signal. When using the external DTACK signal

as a data acknowledge signal, the bus time-out monitor generates a bus error when a bus cycle is

not terminated by the external DTACK signal after 1022 clock counts have elapsed.

Bootstrap

BOOT [3:0]

System Boot Mode Select—The operational system boot mode of the i.MX processor upon system

reset is determined by the settings of these pins.

SDRAM Controller

SDBA [4:0]

SDRAM non-interleave mode bank address multiplexed with address signals A [15:11]. These

signals are logically equivalent to core address p_addr [25:21] in SDRAM cycles.

SDIBA [3:0]

SDRAM interleave addressing mode bank address multiplexed with address signals A [19:16]. These

signals are logically equivalent to core address p_addr [12:9] in SDRAM cycles.

MA [11:10]

SDRAM address signals

MA [9:0]

SDRAM address signals which are multiplexed with address signals A [10:1]. MA [9:0] are selected

on SDRAM cycles.

DQM [3:0]

SDRAM data enable

CSD0

SDRAM Chip-select signal which is multiplexed with the CS2 signal. These two signals are

selectable by programming the system control register.

CSD1

SDRAM Chip-select signal which is multiplexed with CS3 signal. These two signals are selectable by

programming the system control register. By default, CSD1 is selected, so it can be used as boot

chip-select by properly configuring BOOT [3:0] input pins.

RAS

SDRAM Row Address Select signal

相关PDF资料 |

PDF描述 |

|---|---|

| MC9328MXSCVP10R2 | 32-BIT, 100 MHz, MICROPROCESSOR, PBGA225 |

| MC94MX21DVKN3R2 | 350 MHz, MICROPROCESSOR, PBGA289 |

| MC9S08FL8CLC | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, QFP32 |

| MC9S08FL8CBM | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDIP32 |

| MC9S08FL16CBM | 8-BIT, FLASH, 20 MHz, MICROCONTROLLER, PDIP32 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MC9328MXSCVF10(R2) | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Advance Information |

| MC9328MXSCVF10R2 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:Advance Information |

| MC9328MXSCVP10 | 功能描述:处理器 - 专门应用 REDUCED FEATURE I.MXL RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MC9328MXSCVP10R2 | 功能描述:处理器 - 专门应用 REDUCED FEATURE I.MXL RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

| MC9328MXSVP10 | 功能描述:处理器 - 专门应用 REDUCED FEATURE CORSICA RoHS:否 制造商:Freescale Semiconductor 类型:Multimedia Applications 核心:ARM Cortex A9 处理器系列:i.MX6 数据总线宽度:32 bit 最大时钟频率:1 GHz 指令/数据缓存: 数据 RAM 大小:128 KB 数据 ROM 大小: 工作电源电压: 最大工作温度:+ 95 C 安装风格:SMD/SMT 封装 / 箱体:MAPBGA-432 |

发布紧急采购,3分钟左右您将得到回复。