- 您现在的位置:买卖IC网 > PDF目录80349 > MIP7365-450F24M 64-BIT, 450 MHz, MICROPROCESSOR, CQFP208 PDF资料下载

参数资料

| 型号: | MIP7365-450F24M |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 64-BIT, 450 MHz, MICROPROCESSOR, CQFP208 |

| 封装: | 1.20 X 1.20 MM, CERAMIC, QFP-208 |

| 文件页数: | 11/16页 |

| 文件大小: | 285K |

| 代理商: | MIP7365-450F24M |

4

SCD7365 Rev B 1/11/07

Aeroflex Plainview

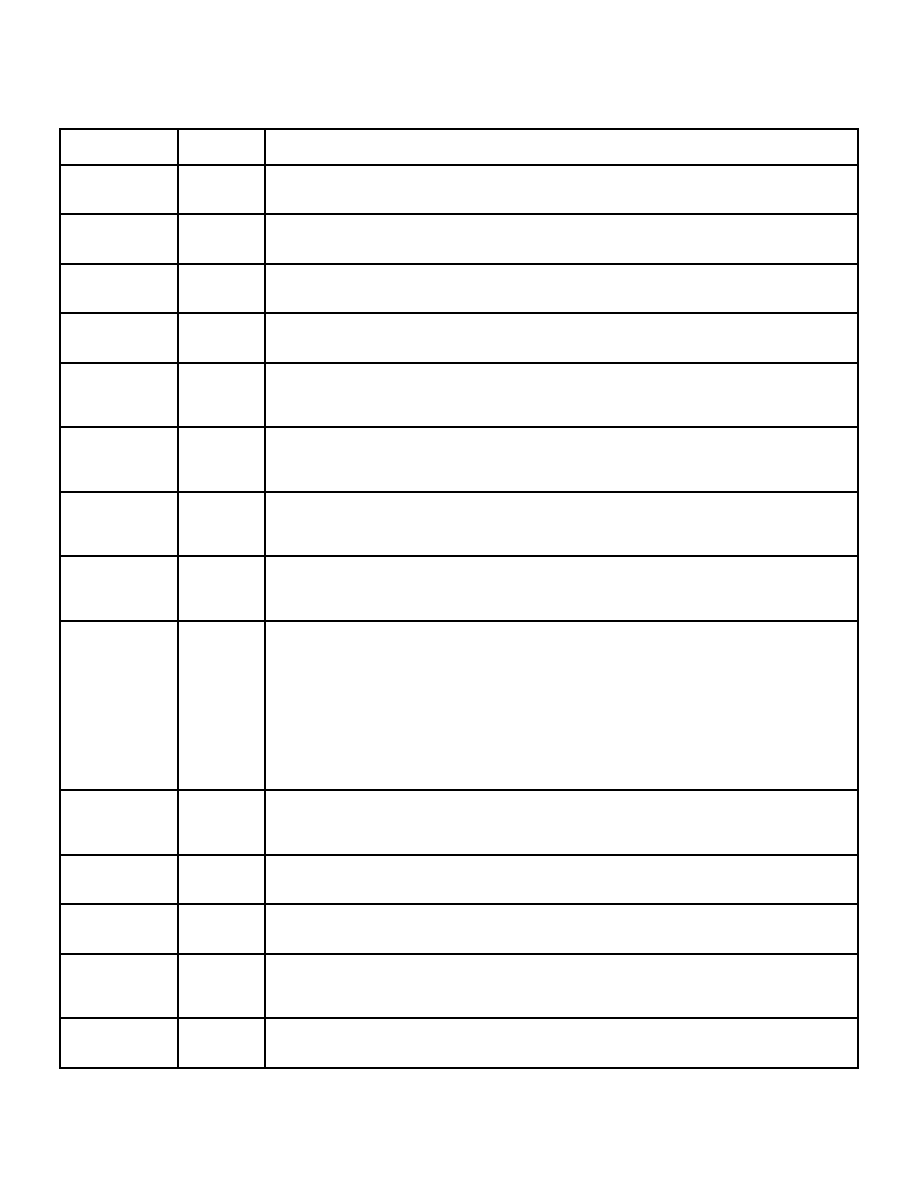

PIN DESCRIPTIONS

The following is a list of control, data, clock, interrupt, and miscellaneous pins of MIP7365.

System Interface

PIN NAME

TYPE

DESCRIPTION

ExtRqst*

Input

External request

Signals that the external agent is submitting an external request.

Release*

Output

Release interface

Signals that the processor is releasing the system interface to slave state

RdRdy*

Input

Read Ready

Signals that an external agent can now accept a processor read.

WrRdy*

Input

Write Ready

Signals that an external agent can now accept a processor write request.

ValidIn*

Input

Valid Input

Signals that an external agent is now driving a valid address or data on the bus and a valid

command or data identifier on the SysCmd bus.

ValidOut*

Output

Valid output

Signals that the processor is now driving a valid address or data on the SysAD bus and a valid

command or data identifier on the SysCmd bus.

PRqst*

Output

Processor Request

When asserted this signal requests that control of the system interface be returned to the

processor. This is enabled by Mode Bit 26

PAck*

Input

Processor Acknowledge

When asserted, in response to PRqst*, this signal indicates to the processor that it has been

granted control of the system interface.

RspSwap*

Input

Response Swap

RspSwap* is used by the external agent to signal the processor when it is about to return a

memory reference out of order; i.e., of two outstanding memory references, the data for the

second reference is being returned ahead of the data for the first reference. In order that the

processor will have time to switch the address to the tertiary cache, this signal must be asserted

a minimum of two cycles prior to the data itself being presented. Note that this signal works as

a toggle; i.e., for each cycle that it is held asserted the order of return is reversed. By default,

anytime the processor issues a second read it is assumed that the reads will be returned in

order; i.e., no action is required if the reads are indeed returned in order. This is enabled by

Mode Bit 26.

RdType

Output

Read Type

During the address cycle of a read request, RdType indicates whether the read request is an

instruction read or a data read.

SysAD[63:0]

Input/Output

System address/data bus

A 64-bit address and data bus for communication between the processor and an external agent.

SysADC[7:0]

Input/Output

System address/data check bus

An 8-bit bus containing parity check bits for the SysAD bus during data cycles.

SysCmd[8:0]

Input/Output

System command/data identifier bus

A 9-bit bus for command and data identifier transmission between the processor and an

external agent.

SysCmdP

Input/Output

System Command/Data Identifier Bus Parity

For the MIP7365, unused on input and zero on output.

相关PDF资料 |

PDF描述 |

|---|---|

| MPC8543EHXANG | 32-BIT, 800 MHz, MICROPROCESSOR, CBGA783 |

| MC912XDP512J1MAL | 16-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQFP112 |

| MPC8543CVTAQG | 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 |

| MPC8543EVTAQG | 32-BIT, 1000 MHz, MICROPROCESSOR, PBGA783 |

| MPC8545CPXANGA | 32-BIT, 800 MHz, MICROPROCESSOR, PBGA783 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MIP803 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Silicon MOS IC |

| MIP804 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Silicon MOS IC |

| MIP805 | 制造商:PANASONIC 制造商全称:Panasonic Semiconductor 功能描述:Silicon MOS IC |

| MIPAQ | 制造商:INFINEON 制造商全称:Infineon Technologies AG 功能描述:Infi neon’s functional IGBT module family |

| MI-PC201-IWY-CC | 制造商:Vicor Corporation 功能描述:MI-PC Series 100W Dual Output 5V 12V DC-DC |

发布紧急采购,3分钟左右您将得到回复。