- 您现在的位置:买卖IC网 > PDF目录45372 > MPC8572PXAULB (FREESCALE SEMICONDUCTOR INC) 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 PDF资料下载

参数资料

| 型号: | MPC8572PXAULB |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 |

| 封装: | 33 X 33 MM, PLASTIC, FCBGA-1023 |

| 文件页数: | 64/138页 |

| 文件大小: | 1502K |

| 代理商: | MPC8572PXAULB |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页当前第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页

MPC8572E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 2

Freescale Semiconductor

31

Ethernet: Enhanced Three-Speed Ethernet (eTSEC)

8.2

FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing

Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII and RTBI are presented in this

section.

8.2.1

FIFO AC Specifications

The basis for the AC specifications for the eTSEC’s FIFO modes is the double data rate RGMII and RTBI

specifications, since they have similar performance and are described in a source-synchronous fashion like

FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and

source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the

relevant eTSEC interface. That is, the transmit clock must be applied to the eTSECn’s TSECn_TX_CLK,

while the receive clock must be applied to pin TSECn_RX_CLK. The eTSEC internally uses the transmit

clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back on

the TSECn_GTX_CLK pin (while transmit data appears on TSECn_TXD[7:0], for example). It is intended

that external receivers capture eTSEC transmit data using the clock on TSECn_GTX_CLK as a source-

synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock

is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is a relationship

between the maximum FIFO speed and the platform (CCB) frequency. For more information see

Input high current

(VIN = LVDD, VIN = TVDD)

IIH

—10

μA

Input low current

(VIN = GND)

IIL

–15

—

μA

Note:

1 LV

DD supports eTSECs 1 and 2.

2 TV

DD supports eTSECs 3 and 4 or FEC.

3 Note that the symbol V

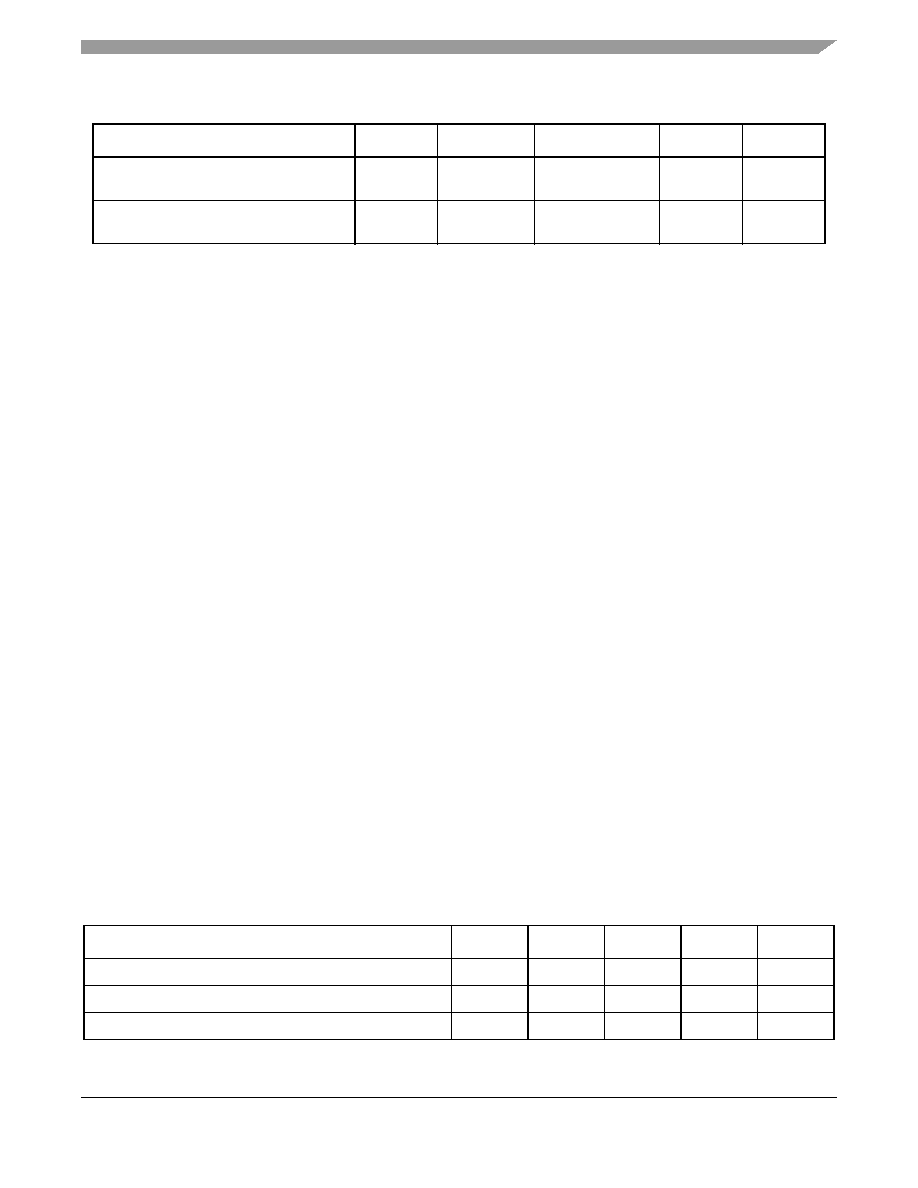

Table 24. FIFO Mode Transmit AC Timing Specification

At recommended operating conditions with LVDD/TVDD of 2.5V ± 5%

Parameter/Condition

Symbol

Min

Typ

Max

Unit

TX_CLK, GTX_CLK clock period1

tFIT

5.3

8.0

100

ns

TX_CLK, GTX_CLK duty cycle

tFITH/tFIT

45

50

55

%

TX_CLK, GTX_CLK peak-to-peak jitter

tFITJ

——

250

ps

Table 23. MII, GMII, RMII, RGMII, TBI, RTBI, and FIFO DC Electrical Characteristics (continued)

Parameters

Symbol

Min

Max

Unit

Notes

相关PDF资料 |

PDF描述 |

|---|---|

| MPC8572CPXAUND | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572ECPXAUNB | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572VTAVLD | 32-BIT, 1500 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572CVTAULD | 32-BIT, 1333 MHz, MICROPROCESSOR, PBGA1023 |

| MPC8572EVTATND | 32-BIT, 1200 MHz, MICROPROCESSOR, PBGA1023 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC8572PXAULD | 功能描述:微处理器 - MPU PQ38H CSM SNPB 1333 RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8572PXAULE | 制造商:Freescale Semiconductor 功能描述:38H R211 NOE SNPB 1333 - Bulk |

| MPC8572PXAVNB | 功能描述:微处理器 - MPU RV1.1.1 SNPB 1500 NOTENC RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8572PXAVND | 功能描述:微处理器 - MPU PQ38H CSM SNPB 1500 RoHS:否 制造商:Atmel 处理器系列:SAMA5D31 核心:ARM Cortex A5 数据总线宽度:32 bit 最大时钟频率:536 MHz 程序存储器大小:32 KB 数据 RAM 大小:128 KB 接口类型:CAN, Ethernet, LIN, SPI,TWI, UART, USB 工作电源电压:1.8 V to 3.3 V 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:FBGA-324 |

| MPC8572PXAVNE | 制造商:Freescale Semiconductor 功能描述:38H R211 NOE SNPB 1500 - Bulk |

发布紧急采购,3分钟左右您将得到回复。