- 您现在的位置:买卖IC网 > PDF目录2014 > MPC9351FA (IDT, Integrated Device Technology Inc)IC PLL CLOCK DRIVER LV 32-LQFP PDF资料下载

参数资料

| 型号: | MPC9351FA |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 14/14页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLOCK DRIVER LV 32-LQFP |

| 标准包装: | 250 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVPECL |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 2:9 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 200MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 2.375 V ~ 3.465 V |

| 工作温度: | -40°C ~ 85°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

MPC9351 REVISION 6 JANUARY 31, 2013

9

2013 Integrated Device Technology, Inc.

MPC9351 Data Sheet

LOW VOLTAGE PLL CLOCK DRIVER

the 100 kHz to 20MHz range; therefore, the filter should be

designed to target this range. The key parameter that needs

to be met in the final filter design is the DC voltage drop

across the series filter resistor (RF). From the data sheet, the

ICCA current (the current sourced through the VCCA pin) is

typically 3mA (5mA maximum), assuming that a minimum of

2.325V (VCC =3.3V or VCC = 2.5V) must be maintained on

resistance of 270

(VCC = 3.3 V) or 9–10 (VCC =2.5 V) to

meet the voltage drop criteria.

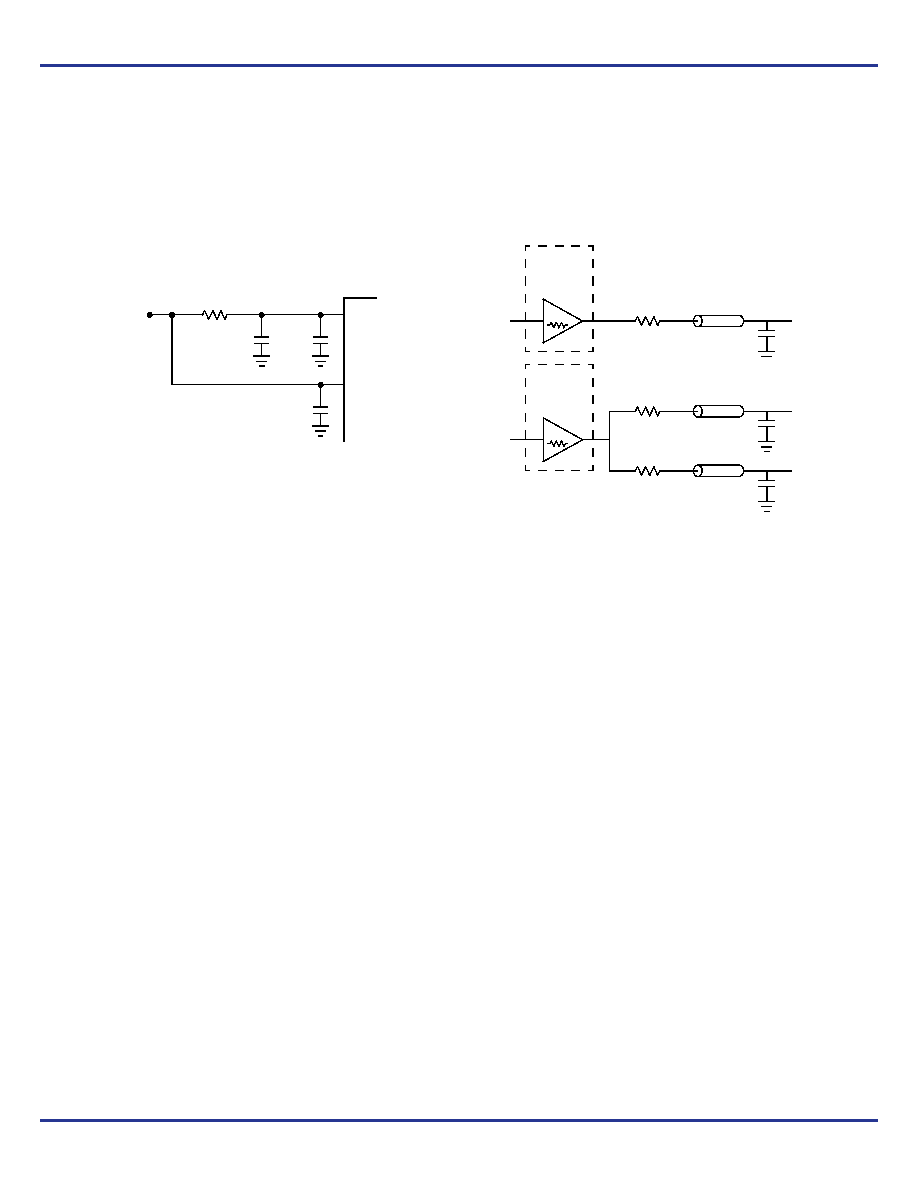

Figure 7. VCCA Power Supply Filter

The minimum values for RF and the filter capacitor CF are

defined by the required filter characteristics. The RC filter

should provide an attenuation greater than 40 dB for noise

whose spectral content is above 100 kHz. In the example RC

filter shown in Figure 7, the filter cut-off frequency is around

3–5 kHz, and the noise attenuation at 100 kHz is better than

42dB.

As the noise frequency crosses the series resonant point

of an individual capacitor, its overall impedance begins to

look inductive, and thus, increases with increasing frequency.

The parallel capacitor combination shown ensures that a low

impedance path to ground exists for frequencies well above

the bandwidth of the PLL. Although the MPC9351 has

several design features to minimize the susceptibility to

power supply noise (isolated power and grounds and fully

differential PLL), there still may be applications in which

overall performance is being degraded due to system power

supply noise. The power supply filter schemes discussed in

this section should be adequate to eliminate power supply

noise related problems in most designs.

Driving Transmission Lines

The MPC9351 clock driver was designed to drive high-

speed signals in a terminated transmission line environment.

To provide the optimum flexibility to the user, the output

drivers were designed to exhibit the lowest impedance

possible. With an output impedance of less than 20

the

drivers can drive either parallel or series terminated

transmission lines. For more information on transmission

lines the reader is referred to Freescale application note

AN1091. In most high performance clock networks,

point-to-point distribution of signals is the method of choice.

In a point-to-point scheme, either series terminated or parallel

terminated transmission lines can be used. The parallel

technique terminates the signal at the end of the line with a

50

resistance to VCC 2.

This technique draws a fairly high level of DC current and

thus only a single terminated line can be driven by each

output of the MPC9351 clock driver. For the series terminated

case, however, there is no DC current draw, thus the outputs

can drive multiple series terminated lines. Figure 8 illustrates

an output driving a single series terminated line versus two

series terminated lines in parallel. When taken to its extreme,

the fanout of the MPC9351 clock driver is effectively doubled

due to its capability to drive multiple lines.

Figure 8. Single versus Dual Transmission Lines

The waveform plots in Figure 9 show the simulation

results of an output driving a single line versus two lines. In

both cases, the drive capability of the MPC9351 output buffer

is more than sufficient to drive 50

transmission lines on the

incident edge. Note from the delay measurements in the

simulations, a delta of only 43ps exists between the two

differently loaded outputs. This suggests that dual line driving

need not be used exclusively to maintain the tight

output-to-output skew of the MPC9351. The output waveform

in Figure 9 shows a step in the waveform. This step is caused

by the impedance mismatch seen looking into the driver. The

parallel combination of the 36

series resistor plus the output

impedance does not match the parallel combination of the

line impedances. The voltage wave launched down the two

lines will equal:

VL =VS (Z0 (RS + R0 + Z0))

Z0 =50 || 50

RS =36 || 36

R0 =14

VL = 3.0 (25 (18 + 17 + 25)

=1.31 V

At the load end, the voltage will double, due to the near

unity reflection coefficient, to 2.6V. It will then increment

towards the quiescent 3.0V in steps separated by one round

trip delay (in this case 4.0ns).

VCCA

VCC

MPC9351

10 nF

RF = 270 for VCC = 3.3 V

RF = 9–10 for VCC = 2.5 V

CF

33...100 nF

RF

VCC

CF = 1 F for VCC = 3.3 V

CF = 22 F for VCC = 2.5 V

14

IN

MPC9351

Output

Buffer

RS = 36

ZO = 50

OutA

14

IN

MPC9351

Output

Buffer

RS = 36

ZO = 50

OutB0

RS = 36

ZO = 50

OutB1

相关PDF资料 |

PDF描述 |

|---|---|

| MPC9352AC | IC CLK GEN ZD 1:11 32-LQFP |

| MPC93H51AC | IC PLL CLK DRIVER LV 32-LQFP |

| MPC93H52AC | IC CLK GEN ZD 1:11 32-LQFP |

| MPC93R51AC | IC PLL CLK DRIVER LV 32-LQFP |

| MPC9608AC | IC CLOCK BUFFER ZD 1:10 32-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9351FAR2 | 功能描述:IC PLL CLOCK DRIVER LV 32-LQFP RoHS:否 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| MPC9352 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:3.3V / 2.5V 1:11 LVCMOS ZERO DELAY CLOCK GENERATOR |

| MPC9352AC | 功能描述:锁相环 - PLL 3.3V 240MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

| MPC9352ACR2 | 功能描述:时钟发生器及支持产品 FSL 1-11 LVCMOS PLL Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9352FA | 功能描述:锁相环 - PLL 2.5 3.3V 200MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:PLL Clock Multiplier 电路数量:1 最大输入频率:710 MHz 最小输入频率:0.002 MHz 输出频率范围:0.002 MHz to 808 MHz 电源电压-最大:3.63 V 电源电压-最小:1.71 V 最大工作温度:+ 85 C 最小工作温度:- 40 C 封装 / 箱体:QFN-36 封装:Tray |

发布紧急采购,3分钟左右您将得到回复。