- 您现在的位置:买卖IC网 > PDF目录2099 > MPC9653AAC (IDT, Integrated Device Technology Inc)IC PLL CLK GEN 1:8 3.3V 32-LQFP PDF资料下载

参数资料

| 型号: | MPC9653AAC |

| 厂商: | IDT, Integrated Device Technology Inc |

| 文件页数: | 6/12页 |

| 文件大小: | 0K |

| 描述: | IC PLL CLK GEN 1:8 3.3V 32-LQFP |

| 标准包装: | 250 |

| 类型: | PLL 时钟发生器 |

| PLL: | 带旁路 |

| 输入: | LVCMOS,LVPECL |

| 输出: | LVCMOS |

| 电路数: | 1 |

| 比率 - 输入:输出: | 1:8 |

| 差分 - 输入:输出: | 是/无 |

| 频率 - 最大: | 125MHz |

| 除法器/乘法器: | 是/无 |

| 电源电压: | 3.135 V ~ 3.465 V |

| 工作温度: | 0°C ~ 70°C |

| 安装类型: | 表面贴装 |

| 封装/外壳: | 32-LQFP |

| 供应商设备封装: | 32-TQFP(7x7) |

| 包装: | 托盘 |

MPC9653A REVISION 4 JANUARY 8, 2013

3

2013 Integrated Device Technology, Inc.

MPC9653A Data Sheet

3.3 V 1:8 LVCMOS PLL CLOCK GENERATOR

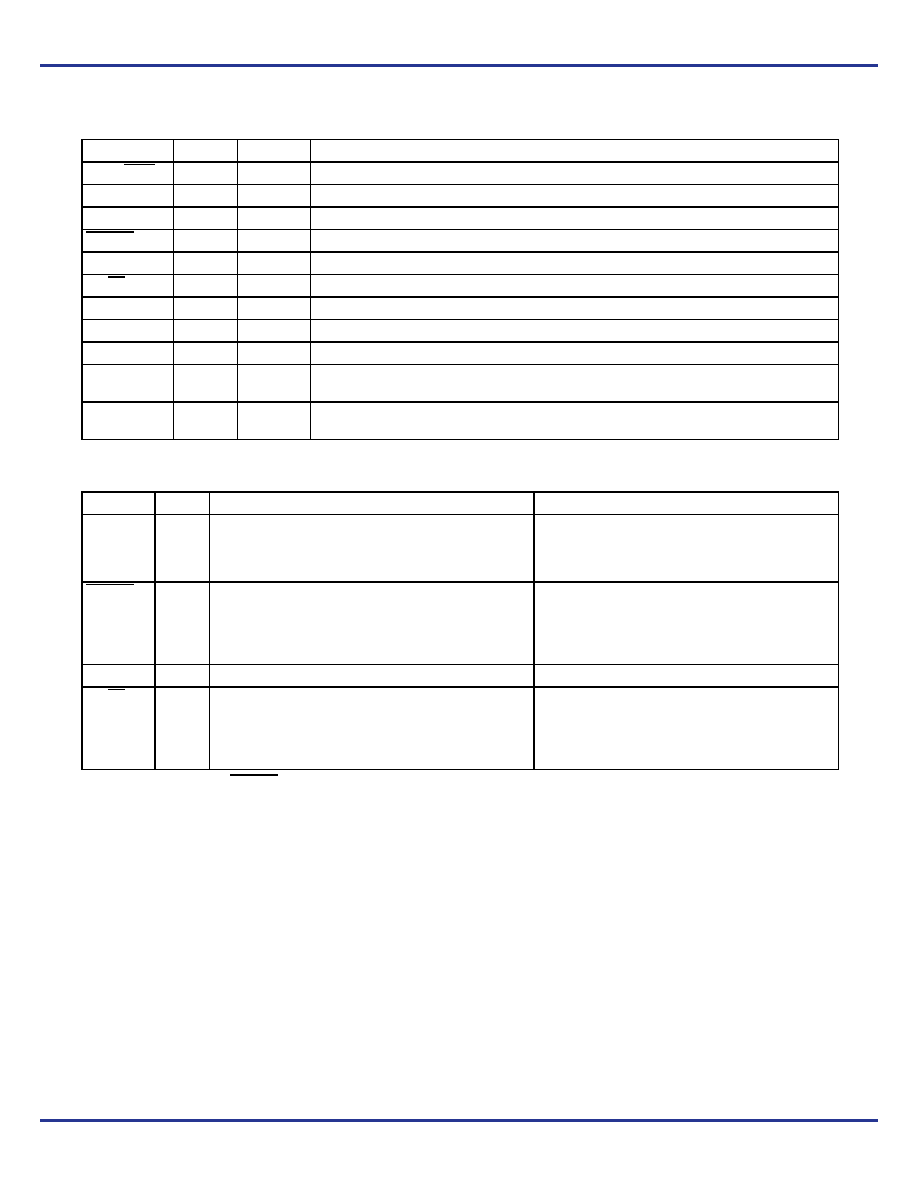

Table 1. Pin Configuration

Pin

I/O

Type

Function

PCLK, PCLK

Input

LVPECL

PECL reference clock signal

FB_IN

Input

LVCMOS

PLL feedback signal input, connect to QFB

VCO_SEL

Input

LVCMOS

Operating frequency range select

BYPASS

Input

LVCMOS

PLL and output divider bypass select

PLL_EN

Input

LVCMOS

PLL enable/disable

MR/OE

Input

LVCMOS

Output enable/disable (high-impedance tristate) and device reset

Q0–7

Output

LVCMOS

Clock outputs

QFB

Output

LVCMOS

Clock output for PLL feedback, connect to FB_IN

GND

Supply

Ground

Negative power supply (GND)

VCC_PLL

Supply

VCC

PLL positive power supply (analog power supply). It is recommended to use an external RC filter for

VCC

Supply

VCC

Positive power supply for I/O and core. All VCC pins must be connected to the positive power supply

for correct operation

Table 2. Function Table

Control

Default

0

1

PLL_EN

1

Test mode with PLL bypassed. The reference clock (PCLK)

is substituted for the internal VCO output. MPC9653A is fully

static and no minimum frequency limit applies. All PLL

related AC characteristics are not applicable.

Selects the VCO output(1)

1. PLL operation requires BYPASS = 1 and PLL_EN = 1.

BYPASS

1

Test mode with PLL and output dividers bypassed. The

reference clock (PCLK) is directly routed to the outputs.

MPC9653A is fully static and no minimum frequency limit

applies. All PLL related AC characteristics are not

applicable.

Selects the output dividers.

VCO_SEL

1

VCO

1 (High frequency range). fREF =fQ0–7 =4 fVCO

VCO

2 (Low output range). fREF = fQ0–7 =8 fVCO

MR/OE

0

Outputs enabled (active)

Outputs disabled (high-impedance state) and reset of

the device. During reset the PLL feedback loop is open.

The VCO is tied to its lowest frequency. The length of the

reset pulse should be greater than one reference clock

cycle (PCLK).

相关PDF资料 |

PDF描述 |

|---|---|

| MPC9658AC | IC PLL CLK GEN 1:10 3.3V 32-LQFP |

| MPC9772FA | IC PLL CLK GEN 1:12 3.3V 52-LQFP |

| MPC9774FAR2 | IC PLL CLK GEN 1:14 3.3V 52-LQFP |

| MPC97H74AE | IC PLL CLK GEN 1:14 3.3V 52-LQFP |

| MPC9993AC | IC PLL CLK DRIVER IDCS 32-LQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MPC9653AAC/W | 功能描述:IC PLL CLK GEN 1:8 3.3V 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| MPC9653AACR2 | 功能描述:时钟发生器及支持产品 RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9653AACR2/W | 功能描述:IC PLL CLK GEN 1:8 3.3V 32-LQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 时钟发生器,PLL,频率合成器 系列:- 标准包装:2,000 系列:- 类型:PLL 时钟发生器 PLL:带旁路 输入:LVCMOS,LVPECL 输出:LVCMOS 电路数:1 比率 - 输入:输出:2:11 差分 - 输入:输出:是/无 频率 - 最大:240MHz 除法器/乘法器:是/无 电源电压:3.135 V ~ 3.465 V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:32-LQFP 供应商设备封装:32-TQFP(7x7) 包装:带卷 (TR) |

| MPC9653AC | 功能描述:时钟发生器及支持产品 3.3V 125MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

| MPC9653AFA | 功能描述:时钟发生器及支持产品 3.3V 125MHz Clock Generator RoHS:否 制造商:Silicon Labs 类型:Clock Generators 最大输入频率:14.318 MHz 最大输出频率:166 MHz 输出端数量:16 占空比 - 最大:55 % 工作电源电压:3.3 V 工作电源电流:1 mA 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:QFN-56 |

发布紧急采购,3分钟左右您将得到回复。