- 您现在的位置:买卖IC网 > PDF目录385639 > MT46V32M4TG-75L (Micron Technology, Inc.) DOUBLE DATA RATE DDR SDRAM PDF资料下载

参数资料

| 型号: | MT46V32M4TG-75L |

| 厂商: | Micron Technology, Inc. |

| 英文描述: | DOUBLE DATA RATE DDR SDRAM |

| 中文描述: | 双倍数据速率的DDR SDRAM内存 |

| 文件页数: | 11/68页 |

| 文件大小: | 2547K |

| 代理商: | MT46V32M4TG-75L |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页当前第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页

11

128Mb: x4, x8, x16 DDR SDRAM

128Mx4x8x16DDR_C.p65

–

Rev. C; Pub. 4/01

Micron Technology, Inc., reserves the right to change products or specifications without notice.

2001, Micron Technology, Inc.

128Mb: x4, x8, x16

DDR SDRAM

PRELIMINARY

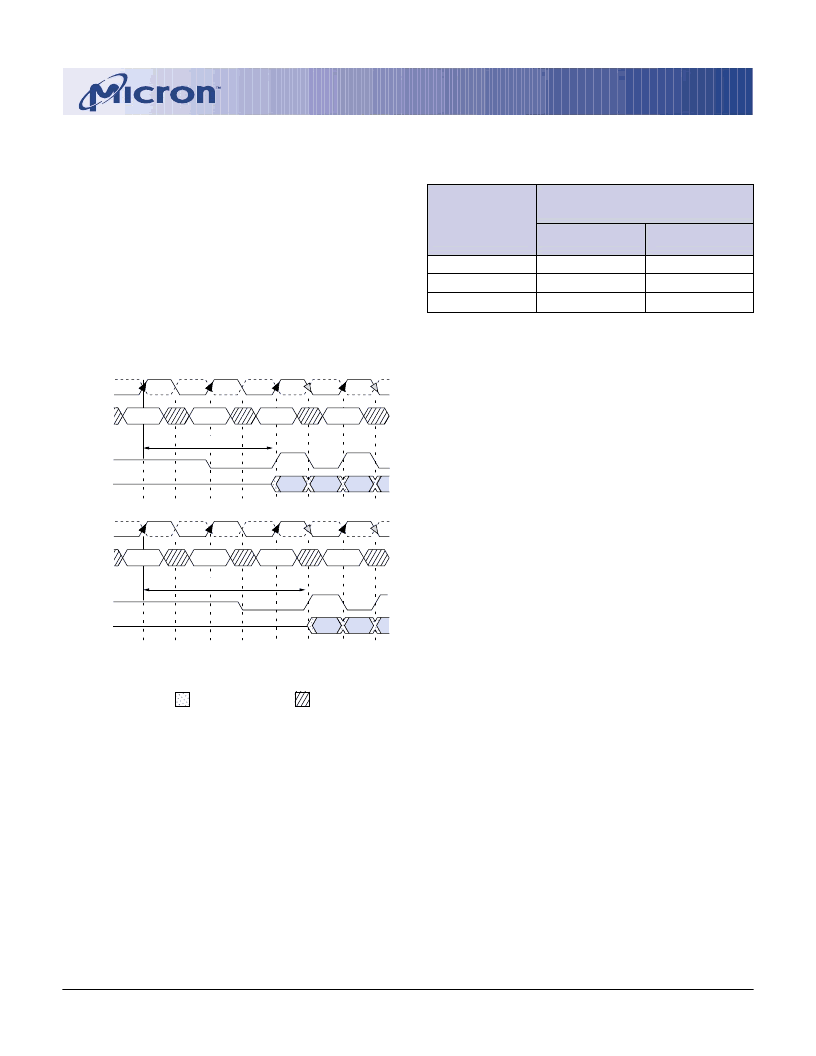

ALLOWABLE OPERATING

FREQUENCY (MHz)

SPEED

-75Z

-75

-8

CL = 2

75

≤

f

≤

133

75

≤

f

≤

100

75

≤

f

≤

100

CL = 2.5

75

≤

f

≤

133

75

≤

f

≤

133

75

≤

f

≤

125

CK

CK#

COMMAND

DQ

DQS

CL = 2

READ

NOP

NOP

NOP

READ

NOP

NOP

NOP

Burst Length = 4 in the cases shown

Shown with nominal tAC and nominal tDSDQ

CK

CK#

COMMAND

DQ

DQS

CL = 2.5

T0

T1

T2

T2n

T3

T3n

T0

T1

T2

T2n

T3

T3n

DON

’

T CARE

TRANSITIONING DATA

TABLE 2

CAS LATENCY (CL)

Read Latency

The READ latency is the delay, in clock cycles,

between the registration of a READ command and the

availability of the first bit of output data. The latency

can be set to 2 or 2.5 clocks, as shown in Figure 2.

If a READ command is registered at clock edge

n

,

and the latency is

m

clocks, the data will be available

nominally coincident with clock edge

n + m

. Table 2

indicates the operating frequencies at which each CAS

latency setting can be used.

Reserved states should not be used as unknown

operation or incompatibility with future versions may

result.

Figure 2

CAS Latency

Operating Mode

The normal operating mode is selected by issuing a

MODE REGISTER SET command with bits A7-A11

each set to zero, and bits A0-A6 set to the desired values.

A DLL reset is initiated by issuing a MODE REGISTER

SET command with bits A7 and A9-A11 each set to

zero, bit A8 set to one, and bits A0-A6 set to the desired

values. Although not required by the Micron device,

JEDEC specifications recommend when a LOAD MODE

REGISTER command is issued to reset the DLL, it

should always be followed by a LOAD MODE REGIS-

TER command to select normal operating mode.

All other combinations of values for A7-A11 are

reserved for future use and/or test modes. Test modes

and reserved states should not be used because un-

known operation or incompatibility with future ver-

sions may result.

相关PDF资料 |

PDF描述 |

|---|---|

| MT46V32M4TG-75Z | DOUBLE DATA RATE DDR SDRAM |

| MT46V32M4TG-75ZL | DOUBLE DATA RATE DDR SDRAM |

| MT46V32M4TG-8 | DOUBLE DATA RATE DDR SDRAM |

| MT46V32M4TG-8L | DOUBLE DATA RATE DDR SDRAM |

| MT46V4M32 | DOUBLE DATA RATE DDR SDRAM |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT46V32M4TG-75Z | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

| MT46V32M4TG-75ZL | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

| MT46V32M4TG-8 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

| MT46V32M4TG-8L | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

| MT46V32M8 | 制造商:MICRON 制造商全称:Micron Technology 功能描述:DOUBLE DATA RATE DDR SDRAM |

发布紧急采购,3分钟左右您将得到回复。