- 您现在的位置:买卖IC网 > PDF目录45324 > MT80C31-30R (ATMEL CORP) 8-BIT, 30 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | MT80C31-30R |

| 厂商: | ATMEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, 30 MHz, MICROCONTROLLER, PQFP44 |

| 封装: | 1 MM HEIGHT, QFP-44 |

| 文件页数: | 151/170页 |

| 文件大小: | 4133K |

| 代理商: | MT80C31-30R |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页当前第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页

81

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined by ACIS1 and

ACIS0. The analog comparator interrupt routine is executed if the ACIE bit is set and the I-bit in SREG is set. ACI

is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by

writing a logic one to the flag.

Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is written logic one, the Analog Comparator interrupt request is enabled. When written logic

zero, the interrupt request is disabled.

Bit 2 – ACIC: Analog Comparator Input Capture Enable

When set, this bit enables the input capture function in Timer/Counter0 to be triggered by the analog comparator.

In this case, the comparator output is directly connected to the input capture front-end logic, using the noise can-

celer and edge select features of the Timer/Counter0 input capture interrupt. To make the comparator trigger the

Timer/Counter0 input capture interrupt, the ICIE0 bit in “TIMSK0 – Timer/Counter Interrupt Mask Register 0” must

be set.

When this bit is cleared, no connection between the analog comparator and the input capture function exists.

Bits 1:0 – ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events that trigger the analog comparator interrupt. The different settings

are shown in Table 12-1.

When changing the ACIS1/ACIS0 bits, the analog comparator Interrupt must be disabled by clearing its Interrupt

Enable bit in “ACSR – Analog Comparator Control and Status Register”. Otherwise an interrupt can occur when

the bits are changed.

12.1.2

DIDR0 – Digital Input Disable Register 0

Bits 1:0 – ADC1D, ADC0D: Digital Input Disable

When this bit is set, the digital input buffer on pin AIN1 (ADC1) / AIN0 (ADC0) is disabled and the corresponding

PIN register bit will read as zero. When used as an analog input but not required as a digital input the power con-

sumption in the digital input buffer can be reduced by writing this bit to logic one.

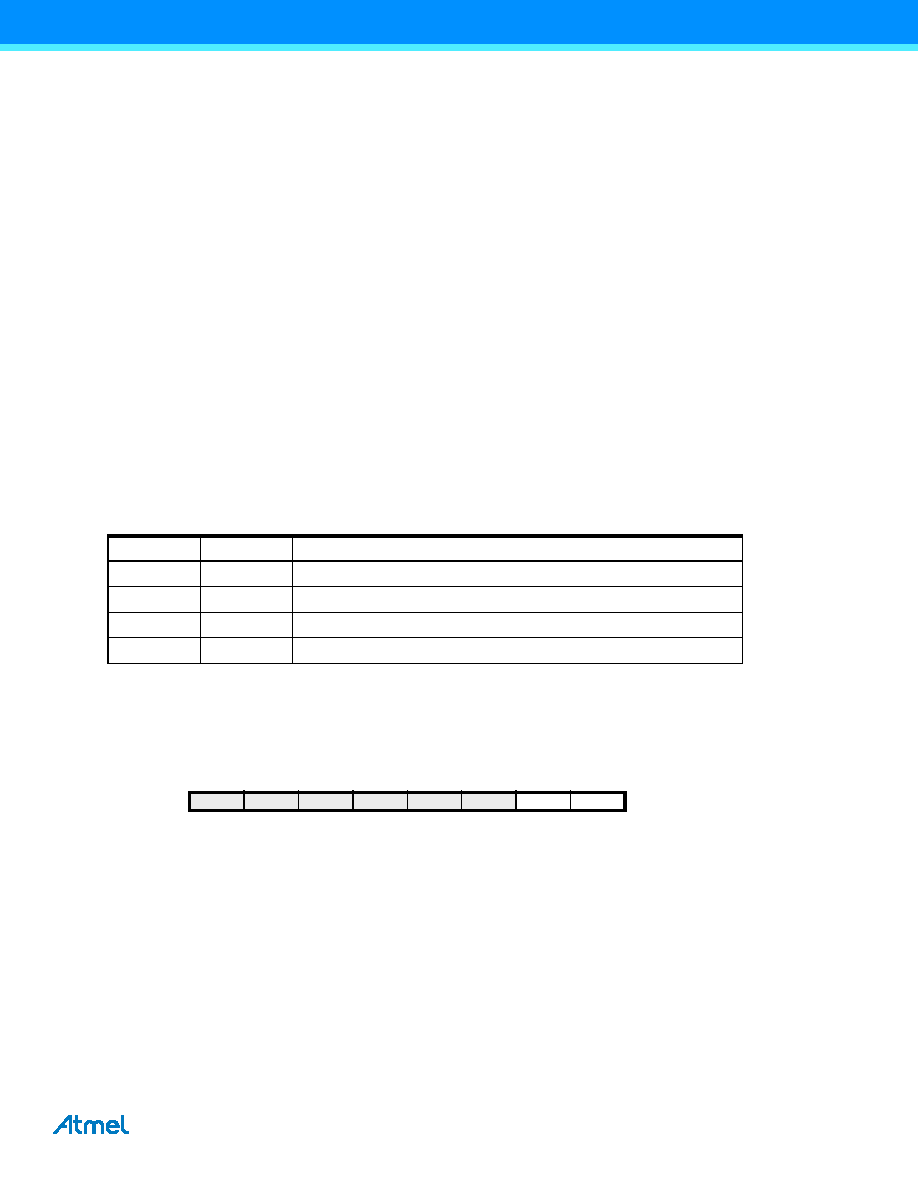

Table 12-1.

Selecting Source for Analog Comparator Interrupt.

ACIS1

ACIS0

Interrupt Mode

0

Comparator Interrupt on Output Toggle.

01

Reserved

1

0

Comparator Interrupt on Falling Output Edge.

1

Comparator Interrupt on Rising Output Edge.

Bit

765

4321

0

–

ADC3D

ADC2D

ADC1D

ADC0D

DIDR0

Read/Write

R

R/W

Initial Value

000

0000

0

相关PDF资料 |

PDF描述 |

|---|---|

| MV80C31-36D | 8-BIT, 36 MHz, MICROCONTROLLER, PQFP44 |

| MS80C51T-30R | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQCC44 |

| MV80C31-30R | 8-BIT, 30 MHz, MICROCONTROLLER, PQFP44 |

| MS80C51C-16R | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQCC44 |

| MF280C31-30R | 8-BIT, 30 MHz, MICROCONTROLLER, PQFP44 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT80C31BH | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Intel 功能描述: |

| MT80C51BH | 制造商:ROCHESTER 制造商全称:ROCHESTER 功能描述:CMOS SINGLE - CHIP 8-BIT MICROCOMPUTER 64K program Memory Space |

| MT80C51FB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT80C51FB/B | 制造商:Intel 功能描述: |

| MT80GB | 制造商:Datak Corporation 功能描述: |

发布紧急采购,3分钟左右您将得到回复。