- 您现在的位置:买卖IC网 > PDF目录45322 > MT80C51T-36D (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 PDF资料下载

参数资料

| 型号: | MT80C51T-36D |

| 厂商: | TEMIC SEMICONDUCTORS |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, MROM, 36 MHz, MICROCONTROLLER, PQFP44 |

| 文件页数: | 166/189页 |

| 文件大小: | 4133K |

| 代理商: | MT80C51T-36D |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页当前第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页

95

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

14. Programming interface

14.1

Features

Physical Layer:

– Synchronous Data Transfer

– Bi-directional, Half-duplex Receiver And Transmitter

– Fixed Frame Format With One Start Bit, 8 Data Bits, One Parity Bit And 2 Stop Bits

– Parity Error Detection, Frame Error Detection And Break Character Detection

– Parity Generation And Collision Detection

– Automatic Guard Time Insertion Between Data Reception And Transmission

Access Layer:

– Communication Based On Messages

– Automatic Exception Handling Mechanism

– Compact Instruction Set

– NVM Programming Access Control

– Tiny Programming Interface Control And Status Space Access Control

– Data Space Access Control

14.2

Overview

The Tiny Programming Interface (TPI) supports external programming of all Non-Volatile Memories (NVM). Mem-

ory programming is done via the NVM Controller, by executing NVM controller commands as described in “Memory

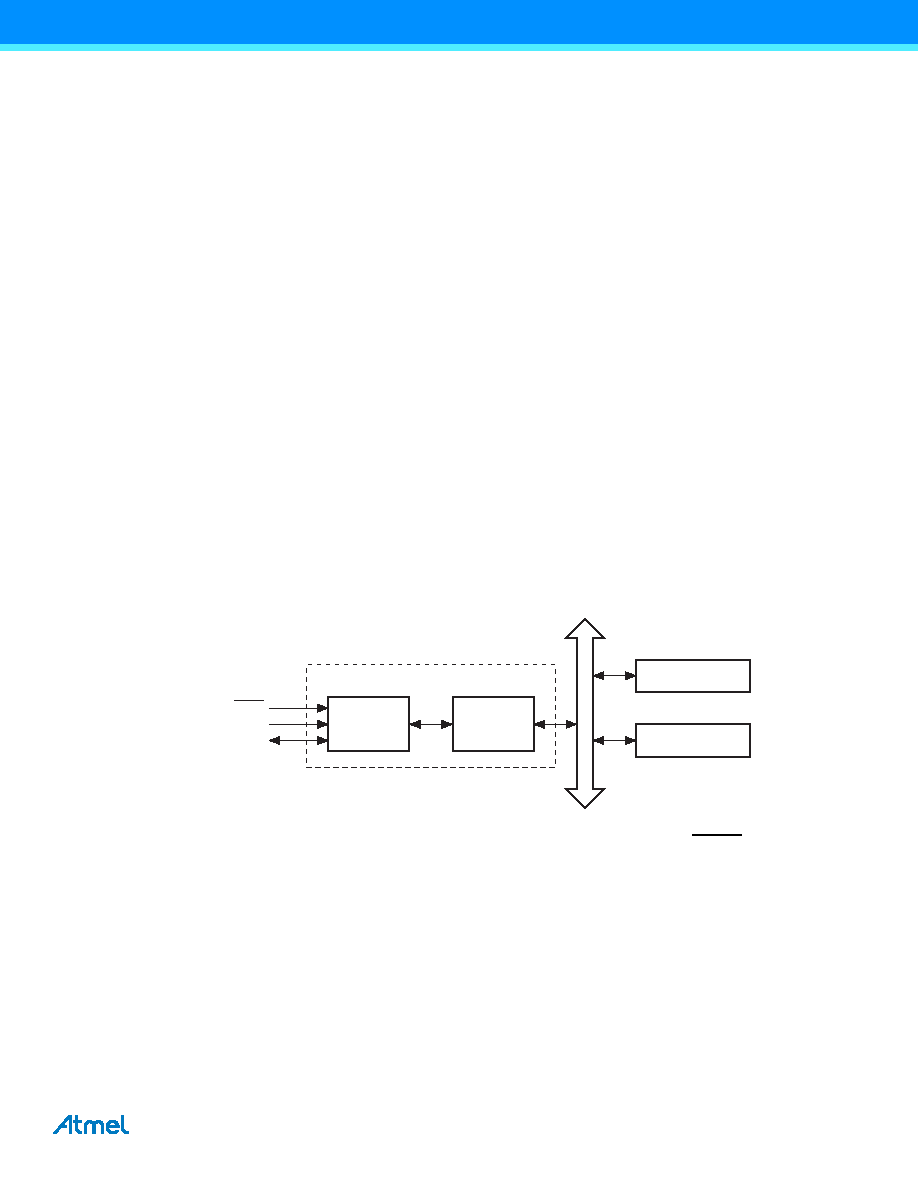

The Tiny Programming Interface (TPI) provides access to the programming facilities. The interface consists of two

layers: the access layer and the physical layer. The layers are illustrated in Figure 14-1.

Figure 14-1. The Tiny Programming Interface and Related Internal Interfaces

Programming is done via the physical interface. This is a 3-pin interface, which uses the RESET pin as enable, the

TPICLK pin as the clock input, and the TPIDATA pin as data input and output.

NVM can be programmed at 5V, only.

14.3

Physical Layer of Tiny Programming Interface

The TPI physical layer handles the basic low-level serial communication. The TPI physical layer uses a bi-direc-

tional, half-duplex serial receiver and transmitter. The physical layer includes serial-to-parallel and parallel-to-serial

data conversion, start-of-frame detection, frame error detection, parity error detection, parity generation and colli-

sion detection.

ACCESS

LAYER

PHYSICAL

LAYER

NVM

CONTROLLER

NON-VOLATILE

MEMORIES

TPICLK

RESET

TPIDATA

TINY PROGRAMMING INTERFACE (TPI)

DATA BUS

相关PDF资料 |

PDF描述 |

|---|---|

| MS80C31-12R | 8-BIT, 12 MHz, MICROCONTROLLER, PQCC44 |

| MT80C51C-12D | 8-BIT, MROM, 12 MHz, MICROCONTROLLER, PQFP44 |

| MS80C31-20R | 8-BIT, 20 MHz, MICROCONTROLLER, PQCC44 |

| MV80C51T-16D | 8-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP44 |

| MP80C31-30D | 8-BIT, 30 MHz, MICROCONTROLLER, PDIP40 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| MT80GB | 制造商:Datak Corporation 功能描述: |

| MT80JSF1G72NDY-1G1F1A2 | 制造商:Micron Technology Inc 功能描述:8GB 1GX72 DDR3 SDRAM MODULE PBF DIMM 1.5V REGISTERED - Trays |

| MT80KSF1G72NDY-1G4F1A3 | 制造商:Micron Technology Inc 功能描述:8GB 1GX72 DDR3 SDRAM MODULE PBF DIMM 1.35V FULLY BUFFERED - Trays |

| MT810 | 制造商:MARKTECH 制造商全称:Marktech Corporate 功能描述:STANDARD T-1 3/4 LED LAMPS |

| MT-8100 | 制造商:Eclipse Tools 功能描述: |

发布紧急采购,3分钟左右您将得到回复。