- 您现在的位置:买卖IC网 > PDF目录69042 > PC34708VK (FREESCALE SEMICONDUCTOR INC) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA206 PDF资料下载

参数资料

| 型号: | PC34708VK |

| 厂商: | FREESCALE SEMICONDUCTOR INC |

| 元件分类: | 电源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PBGA206 |

| 封装: | 8 X 8 MM, 0.50 MM PITCH, LEAD FREE, MO-275CCCE-1, MAPBGA-206 |

| 文件页数: | 10/200页 |

| 文件大小: | 5160K |

| 代理商: | PC34708VK |

第1页第2页第3页第4页第5页第6页第7页第8页第9页当前第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页第190页第191页第192页第193页第194页第195页第196页第197页第198页第199页第200页

Analog Integrated Circuit Device Data

Freescale Semiconductor

107

PC34708

Functional Block Requirements and Behaviors

Mini/Micro USB Interface Description and Application Information

The VUSB regulator defaults to ON when PUMS4:1 = [0100], and is supplied by the SWBST output. As shown in Figure 22 above

this means that the M0 and MOTG switches are open, while the M1 switch is closed.

When PUMS4:1 is not equal to [0100], the VUSB regulator can not be enabled unless 5.0 V is present on the VBUS pin. If VBUS

is detected during a cold start, then the VUSB regulator will be enabled and powered ON in the sequence shown in Power Control

Logic Block Description and Application Information, and it will default to be supplied by the VBUS pin. This means that switch

M0 is closed and switch M1 and MOTG in Figure 22 are open. If VBUS is not detected at cold start, then the VUSB regulator

cannot be enabled. If VBUS is detected later, the VUSB regulator will be enabled automatically be enabled and supplied from

the VBUS pin. The VUSBEN SPI bit is initialized at startup, based on the PUMS4:1 configuration. With PUMS4:1 not equal to

[0100], the VUSBEN SPI bit will default to a one on power up and will reset to a 1, when either RESETB is valid or VBUS is invalid.

This allows the VUSBEN regulator to be enabled automatically if the VUSB regulator was disabled by software. With PUMS4:1

equal to [0100], the VUSBEN bit will be enabled in the power up sequence.

The PC34708 also supports USB OTG mode by supplying 5.0 V to the VBUS pin. The OTGEN SPI bit along with the VUSBSEL

SPI bit, control switching the SWBST to drive VBUS in OTG mode. When OTGEN = 1 and VUSBSEL = 1, SWBST will be driving

the VBUS (switch M1 and MOTG are closed, and the M0 switch is open). In OTG mode, the MVBUS switch should be opened

and the MPD switch closed to isolate the charge input from VBUS. When OTG mode is disabled, the switch (MOTG) from

VINUSB to VBUS will be open.

In OTG mode, the VUSB regulator is enabled by setting the VUSBEN SPI bit to a one. When SWBST is supplying the VBUS pin

(OTG Mode), it will generate a USBDET interrupt. The USBDET interrupt while in OTG mode should not be interpreted as being

powered by the host by software.

Since VBUS is shared with the charger input at the board level (see Battery Management Block Description and Application

Information), the VBUS node must be able to withstand the same high voltages as the charger. The VUSB regulator is disabled

and switches M0 and MOTG are opened in over-voltage conditions.

Table 111. VUSB Input Source Control (68)

Parameter

Value

Function

VUSBSEL

0

Powered by Host: VBUS powers VUSB regulator (switch M0 closed and M1 open)

1

OTG mode: SWBST internally switched to supply the VUSB regulator (switch M1 closed, M0 open), and

SWBST will drive VBUS from the VINUSB pin as long as SPI bit OTGEN is set = 1.

Notes

68.

VUSBSEL = 1 and OTGEN = 1 only close the switch between the VINUSB and VBUS pins, but do not enable the SWBST boost

switcher (which should be enabled with SWBSTEN = 1)

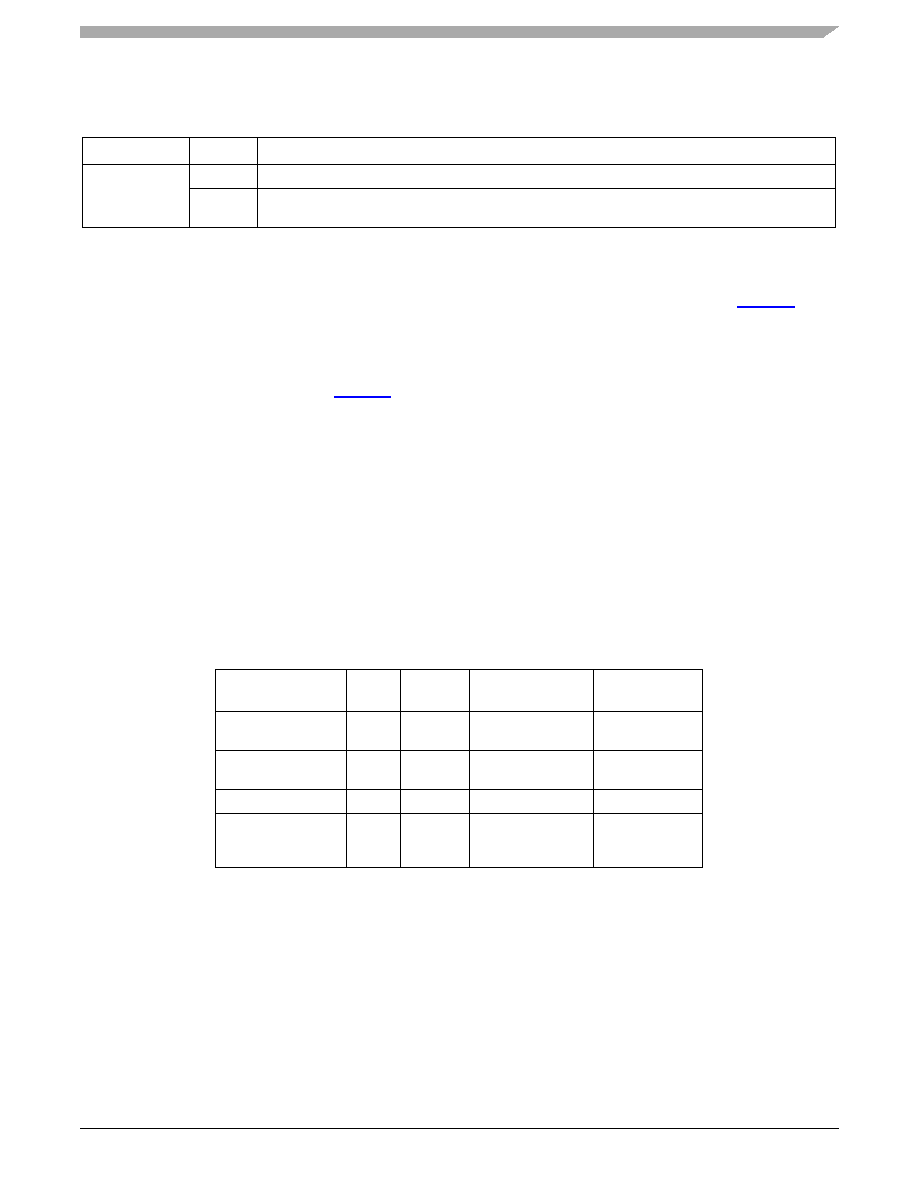

Table 112. VUSB/OTG Switch Configuration

Mode

OTGEN VUSBSEL

Switches Enabled

(Closed)

Switches

Disabled (Open)

VUSB powered from

VBUS pin

0

M0

M1, MOTG

VUSB powered from

VINUSB pin

0

1

M1

M0, MOTG

Invalid option

1

0

OTG Mode (VUSB

powered from VINUSB

pin and SWBST

1

M1, MOTG

M0, MVBUS, MPD

相关PDF资料 |

PDF描述 |

|---|---|

| PCF1252-6T | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO8 |

| PCF1252-8T-T | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO8 |

| PCF1252-4T-T | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO8 |

| PCF1252-4T | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDSO8 |

| PCF1252-7P | 1-CHANNEL POWER SUPPLY SUPPORT CKT, PDIP8 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PC34708VM | 制造商:Freescale Semiconductor 功能描述:PMIC 5S 6LDO BST 10BTADC - Bulk |

| PC34709VK | 制造商:Freescale Semiconductor 功能描述:PMIC 5SW,6 LDO,BST - Bulk |

| PC34709VKR2 | 制造商:Freescale Semiconductor 功能描述:PMIC 5SW,6 LDO,BST - Tape and Reel |

| PC34710EW | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Adjustable Dual Output Switching Power Supply |

| PC34710EWR2 | 制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:Adjustable Dual Output Switching Power Supply |

发布紧急采购,3分钟左右您将得到回复。