- 您现在的位置:买卖IC网 > PDF目录367933 > PH28F256L18T85 (INTEL CORP) StrataFlash Wireless Memory PDF资料下载

参数资料

| 型号: | PH28F256L18T85 |

| 厂商: | INTEL CORP |

| 元件分类: | PROM |

| 英文描述: | StrataFlash Wireless Memory |

| 中文描述: | 16M X 16 FLASH 1.8V PROM, 85 ns, PBGA79 |

| 封装: | 0.75 MM PITCH, LEAD FREE, VFBGA-79 |

| 文件页数: | 31/106页 |

| 文件大小: | 1272K |

| 代理商: | PH28F256L18T85 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页当前第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页

Intel StrataFlash Wireless Memory (L18)

Datasheet

Intel StrataFlash Wireless Memory (L18)

Order Number: 251902, Revision: 009

April 2005

31

7.4

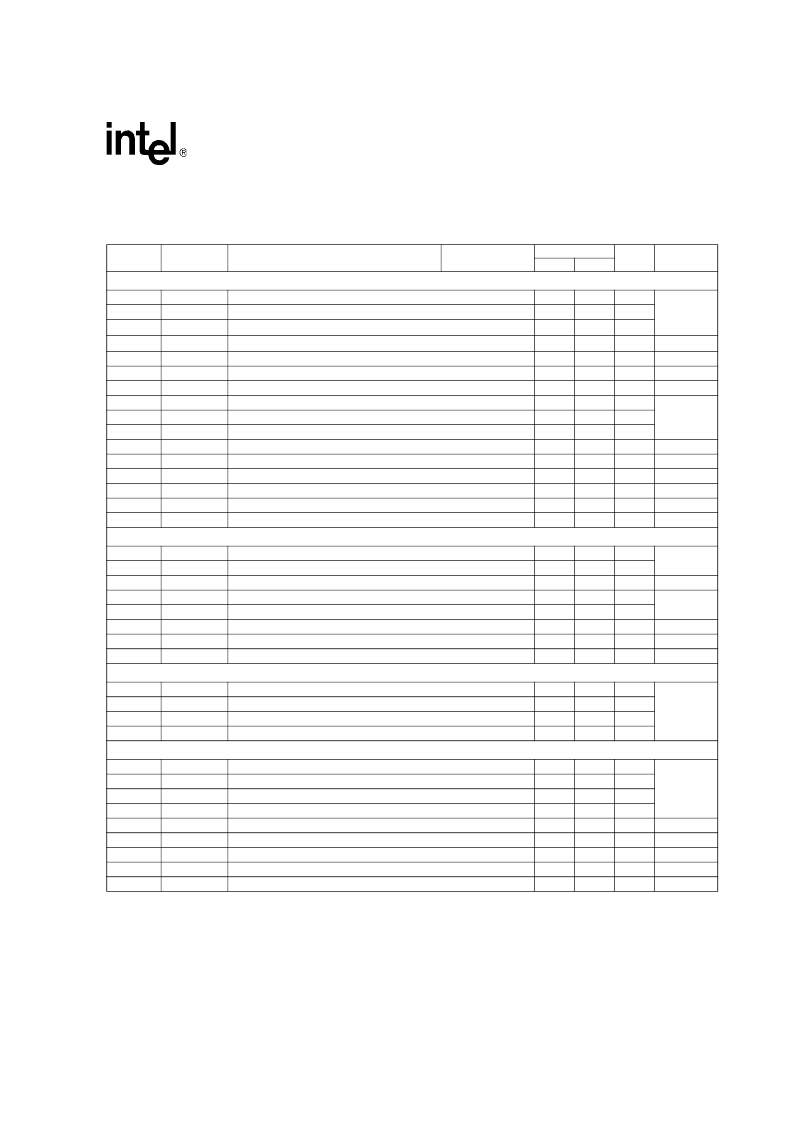

AC Read Specifications for 64-Mbit and 128-Mbit Densities

(V

CCQ

= 1.7 V – 2.0 V)

Num

Symbol

Parameter

Speed

–85

Units

Notes

Min

Max

Asynchronous Specifications

R1

R2

R3

t

AVAV

t

AVQV

t

ELQV

t

GLQV

t

PHQV

t

ELQX

t

GLQX

t

EHQZ

t

GHQZ

t

OH

t

EHEL

t

ELTV

t

EHTZ

t

GLTV

t

GLTX

t

GHTZ

Read cycle time

Address to output valid

CE# low to output valid

85

-

-

-

ns

ns

ns

6

85

85

R4

R5

R6

R7

R8

R9

R10

R11

R12

R13

R15

R16

R17

OE# low to output valid

RST# high to output valid

CE# low to output in low-Z

OE# low to output in low-Z

CE# high to output in high-Z

OE# high to output in high-Z

Output hold from first occurring address, CE#, or OE# change

CE# pulse width high

CE# low to WAIT valid

CE# high to WAIT high Z

OE# low to WAIT valid

OE# low to WAIT in low-Z

OE# high to WAIT in high-Z

-

-

0

0

-

-

0

20

150

-

-

17

17

-

-

14

14

14

-

17

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

1,2

1

1,3

1,2,3

1,3

14

-

-

-

0

-

1

1

1,3

1

1,3

1,3

Latching Specifications

R101

R102

R103

R104

R105

R106

R108

R111

t

AVVH

t

ELVH

t

VLQV

t

VLVH

t

VHVL

t

VHAX

t

APA

t

phvh

Address setup to ADV# high

CE# low to ADV# high

ADV# low to output valid

ADV# pulse width low

ADV# pulse width high

Address hold from ADV# high

Page address access

RST# high to ADV# high

7

-

-

ns

ns

ns

ns

ns

ns

ns

ns

1

10

-

7

7

7

-

30

85

-

-

-

25

-

1,6

1

1,4

1

1

Clock Specifications

R200

R201

R202

R203

f

CLK

t

CLK

t

CH/CL

t

FCLK/RCLK

CLK frequency

CLK period

CLK high/low time

CLK fall/rise time

-

54

-

-

3

MHz

ns

ns

ns

1,3

18.5

3.5

-

Synchronous Specifications

R301

R302

R303

R304

R305

R306

R307

R311

R312

t

AVCH/L

t

VLCH/L

t

ELCH/L

t

CHQV

/ t

CLQV

t

CHQX

t

CHAX

t

CHTV

t

CHVL

t

CHTX

Address setup to CLK

ADV# low setup to CLK

CE# low setup to CLK

CLK to output valid

Output hold from CLK

Address hold from CLK

CLK to WAIT valid

CLK Valid to ADV# Setup

WAIT Hold from CLK

7

7

7

-

3

7

-

0

3

-

-

-

ns

ns

ns

ns

ns

ns

ns

ns

ns

1

14

-

-

14

-

-

1,5

1,4,5

1,5

1

1,5

NOTES:

1.

See

Figure 8, “AC Input/Output Reference Waveform” on page 28

for timing measurements and maximum allowable

input slew rate.

OE# may be delayed by up to t

ELQV

– t

GLQV

after CE#’s falling edge without impact to t

ELQV

.

Sampled, not 100% tested.

Address hold in synchronous burst mode is t

or t

VHAX

, whichever timing specification is satisfied first.

Applies only to subsequent synchronous reads.

The specifications in

Section 7.3

will

only

be used by customers (1) who desire a 1.35 to 2.0 V

operating range OR

(2) who desire to transition their host controller from a 1.7 V to 2.0 V V

CCQ

voltage now to a lower range in the future.

2.

3.

4.

5.

6.

相关PDF资料 |

PDF描述 |

|---|---|

| PH28F640L18B85 | StrataFlash Wireless Memory |

| PH28F640L18T85 | StrataFlash Wireless Memory |

| PH2907A | PNP switching transistor |

| PH2907 | PNP switching transistor |

| PH2931-135S | Rail-to-Rail, Very Low Noise Universal Dual Filter Building Block; Package: SO; No of Pins: 16; Temperature Range: -40°C to +85°C |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PH28F320C3TD70A | 制造商:Micron Technology Inc 功能描述:Flash Mem Parallel 3V/3.3V 32M-Bit 2M x 16 70ns 48-Pin VFBGA Tray 制造商:Micron Technology Inc 功能描述:MM#869664FLASH 28F320C3TD 70 VF-PBGA47 E |

| PH28F320W18BE60A | 制造商:Micron Technology Inc 功能描述:IC FLASH 32MBIT 60NS VFBGA |

| PH28F320W18BE60B | 制造商:Micron Technology Inc 功能描述:32MB, CRYSTAL .75 VFBGA 1.8 LF - Tape and Reel |

| PH28F320W18BE60D | 制造商:Micron Technology Inc 功能描述:32MB, CRYSTAL .75 VFBGA 1.8 LF - Trays |

| PH28F320W18BE60E | 制造商:Micron Technology Inc 功能描述:32MB, CRYSTAL .75 VFBGA 1.8 LF - Tape and Reel |

发布紧急采购,3分钟左右您将得到回复。