- 您现在的位置:买卖IC网 > PDF目录299771 > PIC16C923T-04I/PT 8-BIT, OTPROM, 4 MHz, RISC MICROCONTROLLER, PQFP64 PDF资料下载

参数资料

| 型号: | PIC16C923T-04I/PT |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 8-BIT, OTPROM, 4 MHz, RISC MICROCONTROLLER, PQFP64 |

| 封装: | 10 X 10 MM, 1 MM HEIGHT, PLASTIC, TQFP-64 |

| 文件页数: | 144/189页 |

| 文件大小: | 1201K |

| 代理商: | PIC16C923T-04I/PT |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页当前第144页第145页第146页第147页第148页第149页第150页第151页第152页第153页第154页第155页第156页第157页第158页第159页第160页第161页第162页第163页第164页第165页第166页第167页第168页第169页第170页第171页第172页第173页第174页第175页第176页第177页第178页第179页第180页第181页第182页第183页第184页第185页第186页第187页第188页第189页

PIC16C9XX

DS30444E - page 58

1997 Microchip Technology Inc.

10.1

Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the

16-bit value of the TMR1 register when an event occurs

on pin RC2/CCP1 (Figure 10-2). An event is dened as:

Every falling edge

Every rising edge

Every 4th rising edge

Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0

(CCP1CON<3:0>). When a capture is made, the inter-

rupt request ag bit CCP1IF (PIR1<2>) is set. It must

be cleared in software. If another capture occurs before

the value in register CCPR1 is read, the old captured

value will be lost.

10.1.1

CCP PIN CONFIGURATION

In capture mode, the RC2/CCP1 pin should be cong-

ured as an input by setting the TRISC<2> bit.

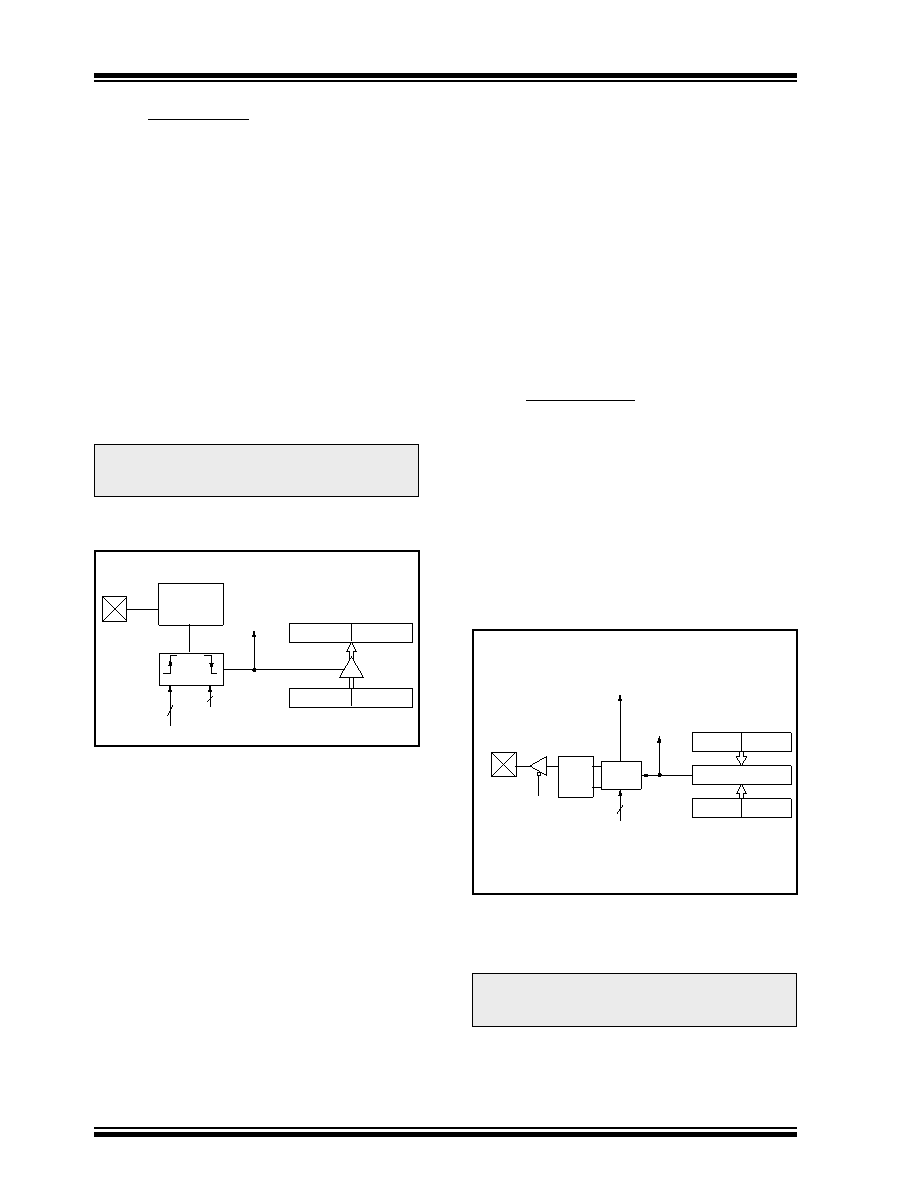

FIGURE 10-2: CAPTURE MODE OPERATION

BLOCK DIAGRAM

10.1.2

TIMER1 MODE SELECTION

Timer1 must be running in timer mode or synchronized

counter mode for the CCP module to use the capture

feature. In asynchronous counter mode the capture

operation may not work.

10.1.3

SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture

interrupt may be generated. The user should keep

enable bit CCP1IE (PIE1<2>) clear to avoid false inter-

rupts and should clear ag bit CCP1IF following any

such change in operating mode.

10.1.4

CCP PRESCALER

There are four prescaler settings, specied by bits

CCP1M3:CCP1M0. Whenever the CCP module is

turned off, or the CCP module is not in Capture mode,

the prescaler counter is cleared. This means that any

reset will clear the prescaler counter.

Note:

If the RC2/CCP1 pin is congured as an

output, a write to the port can cause a cap-

ture condition.

CCPR1H

CCPR1L

TMR1H

TMR1L

Set CCP1IF

PIR1<2>

Capture

Enable

Q’s

CCP1CON<3:0>

RC2/CCP1

Prescaler

÷ 1, 4, 16

and

edge detect

pin

CCP

Switching from one capture prescaler to another may

generate an interrupt. Also, the prescaler counter will

not be cleared, therefore the rst capture may be from

a non-zero prescaler. Example 10-1 shows the recom-

mended method for switching between capture prescal-

ers. This example also clears the prescaler counter and

will not generate the “false” interrupt.

EXAMPLE 10-1: CHANGING BETWEEN

CAPTURE PRESCALERS

CLRF

CCP1CON

; Turn CCP module off

MOVLW

NEW_CAPT_PS ; Load the W reg with

; the new prescaler

; mode value and CCP ON

MOVWF

CCP1CON

; Load CCP1CON with

; this value

10.2

Compare Mode

In Compare mode, the 16-bit CCPR1 register value is

constantly compared against the TMR1 register pair

value. When a match occurs, the RC2/CCP1 pin is:

Driven High

Driven Low

Remains Unchanged

The action on the pin is based on the value of control

bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the

same time, a compare interrupt is also generated.

FIGURE 10-3: COMPARE MODE

OPERATION BLOCK DIAGRAM

10.2.1

CCP PIN CONFIGURATION

The user must congure the RC2/CCP1 pin as an out-

put by clearing the TRISC<2> bit.

Note:

Clearing the CCP1CON register will force

the RC2/CCP1 compare output latch to the

default low level. This is not the data latch.

CCPR1H CCPR1L

TMR1H

TMR1L

Comparator

Q

S

R

Output

Logic

Special event trigger will reset Timer1, but not

T

rigger

Set CCP1IF

PIR1<2>

match

RC2/CCP1

TRISC<2>

CCP1CON<3:0>

Mode Select

Output Enable

set interrupt ag bit TMR1IF (PIR1<0>).

相关PDF资料 |

PDF描述 |

|---|---|

| PIC16C925/L | 8-BIT, OTPROM, 20 MHz, RISC MICROCONTROLLER, PQCC68 |

| PIC16C925/PT | 8-BIT, OTPROM, 20 MHz, RISC MICROCONTROLLER, PQFP64 |

| PIC16LC926-I/PT | 8-BIT, OTPROM, 10 MHz, RISC MICROCONTROLLER, PQFP64 |

| PIC16F1518-I/SO | 8-BIT, FLASH, RISC MICROCONTROLLER, PDSO28 |

| PIC16F1518T-E/MV | RISC MICROCONTROLLER, PQCC28 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC16C923T-08/L | 功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C923T-08/PT | 功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C923T-08I/L | 功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C923T-08I/PT | 功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC16C924/CL | 功能描述:8位微控制器 -MCU 7KB 176 RAM 52 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

发布紧急采购,3分钟左右您将得到回复。