- 您现在的位置:买卖IC网 > PDF目录3830 > PIC18LF2520-I/SP (Microchip Technology)IC MCU FLASH 16KX16 28-DIP PDF资料下载

参数资料

| 型号: | PIC18LF2520-I/SP |

| 厂商: | Microchip Technology |

| 文件页数: | 38/151页 |

| 文件大小: | 0K |

| 描述: | IC MCU FLASH 16KX16 28-DIP |

| 产品培训模块: | Asynchronous Stimulus |

| 标准包装: | 15 |

| 系列: | PIC® 18F |

| 核心处理器: | PIC |

| 芯体尺寸: | 8-位 |

| 速度: | 40MHz |

| 连通性: | I²C,SPI,UART/USART |

| 外围设备: | 欠压检测/复位,HLVD,POR,PWM,WDT |

| 输入/输出数: | 25 |

| 程序存储器容量: | 32KB(16K x 16) |

| 程序存储器类型: | 闪存 |

| EEPROM 大小: | 256 x 8 |

| RAM 容量: | 1.5K x 8 |

| 电压 - 电源 (Vcc/Vdd): | 2 V ~ 5.5 V |

| 数据转换器: | A/D 10x10b |

| 振荡器型: | 内部 |

| 工作温度: | -40°C ~ 85°C |

| 封装/外壳: | 28-DIP(0.300",7.62mm) |

| 包装: | 管件 |

| 产品目录页面: | 643 (CN2011-ZH PDF) |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页当前第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页第130页第131页第132页第133页第134页第135页第136页第137页第138页第139页第140页第141页第142页第143页第144页第145页第146页第147页第148页第149页第150页第151页

2011-2012 Microchip Technology Inc.

Preliminary

DS41579C-page 305

PIC16(L)F1782/3

26.6.10

SLEEP OPERATION

While in Sleep mode, the I2C slave module can receive

addresses or data and when an address match or

complete byte transfer occurs, wake the processor

from Sleep (if the MSSP interrupt is enabled).

26.6.11

EFFECTS OF A RESET

A Reset disables the MSSP module and terminates the

current transfer.

26.6.12

MULTI-MASTER MODE

In Multi-Master mode, the interrupt generation on the

detection of the Start and Stop conditions allows the

determination of when the bus is free. The Stop (P) and

Start (S) bits are cleared from a Reset or when the

MSSP module is disabled. Control of the I2C bus may

be taken when the P bit of the SSPSTAT register is set,

or the bus is Idle, with both the S and P bits clear. When

the bus is busy, enabling the SSP interrupt will gener-

ate the interrupt when the Stop condition occurs.

In multi-master operation, the SDA line must be

monitored for arbitration to see if the signal level is the

expected output level. This check is performed by

hardware with the result placed in the BCLIF bit.

The states where arbitration can be lost are:

Address Transfer

Data Transfer

A Start Condition

A Repeated Start Condition

An Acknowledge Condition

26.6.13

MULTI -MASTER COMMUNICATION,

BUS COLLISION AND BUS

ARBITRATION

Multi-Master mode support is achieved by bus arbitra-

tion. When the master outputs address/data bits onto

the SDA pin, arbitration takes place when the master

outputs a ‘1’ on SDA, by letting SDA float high and

another master asserts a ‘0’. When the SCL pin floats

high, data should be stable. If the expected data on

SDA is a ‘1’ and the data sampled on the SDA pin is ‘0’,

then a bus collision has taken place. The master will set

the Bus Collision Interrupt Flag, BCLIF and reset the

If a transmit was in progress when the bus collision

occurred, the transmission is halted, the BF flag is

cleared, the SDA and SCL lines are deasserted and the

SSPBUF can be written to. When the user services the

bus collision Interrupt Service Routine and if the I2C

bus is free, the user can resume communication by

asserting a Start condition.

If a Start, Repeated Start, Stop or Acknowledge condi-

tion was in progress when the bus collision occurred, the

condition is aborted, the SDA and SCL lines are deas-

serted and the respective control bits in the SSPCON2

register are cleared. When the user services the bus col-

lision Interrupt Service Routine and if the I2C bus is free,

the user can resume communication by asserting a Start

condition.

The master will continue to monitor the SDA and SCL

pins. If a Stop condition occurs, the SSPIF bit will be set.

A write to the SSPBUF will start the transmission of

data at the first data bit, regardless of where the

transmitter left off when the bus collision occurred.

In Multi-Master mode, the interrupt generation on the

detection of Start and Stop conditions allows the deter-

mination of when the bus is free. Control of the I2C bus

can be taken when the P bit is set in the SSPSTAT

register, or the bus is Idle and the S and P bits are

cleared.

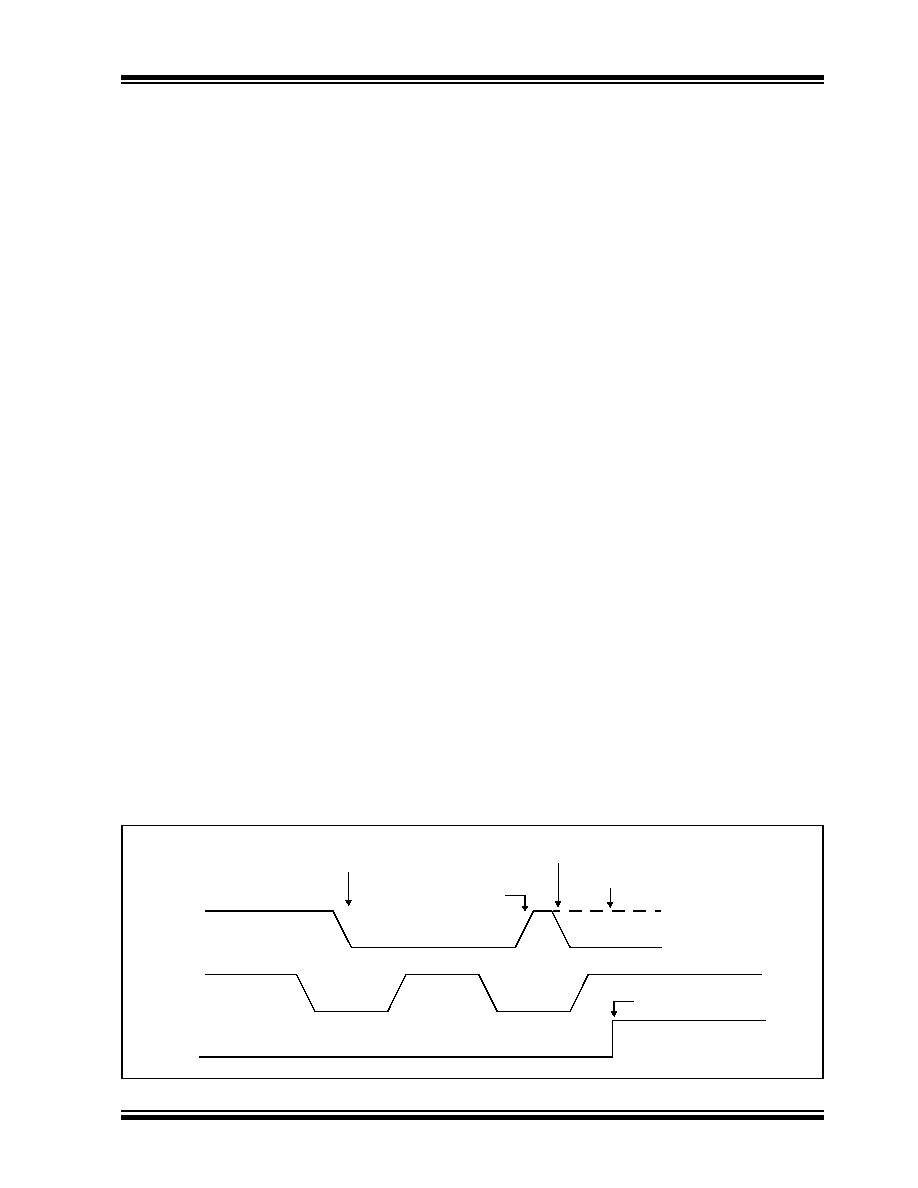

FIGURE 26-32:

BUS COLLISION TIMING FOR TRANSMIT AND ACKNOWLEDGE

SDA

SCL

BCLIF

SDA released

SDA line pulled low

by another source

Sample SDA. While SCL is high,

data does not match what is driven

Bus collision has occurred.

Set bus collision

interrupt (BCLIF)

by the master.

by master

Data changes

while SCL = 0

相关PDF资料 |

PDF描述 |

|---|---|

| PIC24HJ128GP206A-I/PT | IC PIC MCU FLASH 128KB 64-TQFP |

| PIC18LF4423-I/P | IC PIC MCU FLASH 8KX16 40DIP |

| 213684-1 | 34P PLUG KIT,M-SERIES,CC,JS |

| PIC18LF2455-I/SO | IC PIC MCU FLASH 12KX16 28SOIC |

| DSPIC33FJ64GP204-E/PT | IC DSPIC MCU/DSP 64K 44-TQFP |

相关代理商/技术参数 |

参数描述 |

|---|---|

| PIC18LF2520T-I/ML | 功能描述:8位微控制器 -MCU 32KB 1536 RAM 25I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF2520T-I/SO | 功能描述:8位微控制器 -MCU 32KB 1536 RAM 25I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF2523-I/ML | 功能描述:8位微控制器 -MCU 32KB 1536bytes-RAM 25I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF2523-I/SO | 功能描述:8位微控制器 -MCU 32KB 1536bytes-RAM 25I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT |

| PIC18LF2523-I/SO | 制造商:Microchip Technology Inc 功能描述:8-BIT MICROCONTROLLER IC |

发布紧急采购,3分钟左右您将得到回复。