- 您现在的位置:买卖IC网 > PDF目录380637 > R1Q3A3609ABG-60R (Renesas Technology Corp.) 36-Mbit QDR™II SRAM 4-word Burst PDF资料下载

参数资料

| 型号: | R1Q3A3609ABG-60R |

| 厂商: | Renesas Technology Corp. |

| 英文描述: | 36-Mbit QDR™II SRAM 4-word Burst |

| 文件页数: | 16/26页 |

| 文件大小: | 407K |

| 代理商: | R1Q3A3609ABG-60R |

R1Q3A3636/R1Q3A3618/R1Q3A3609

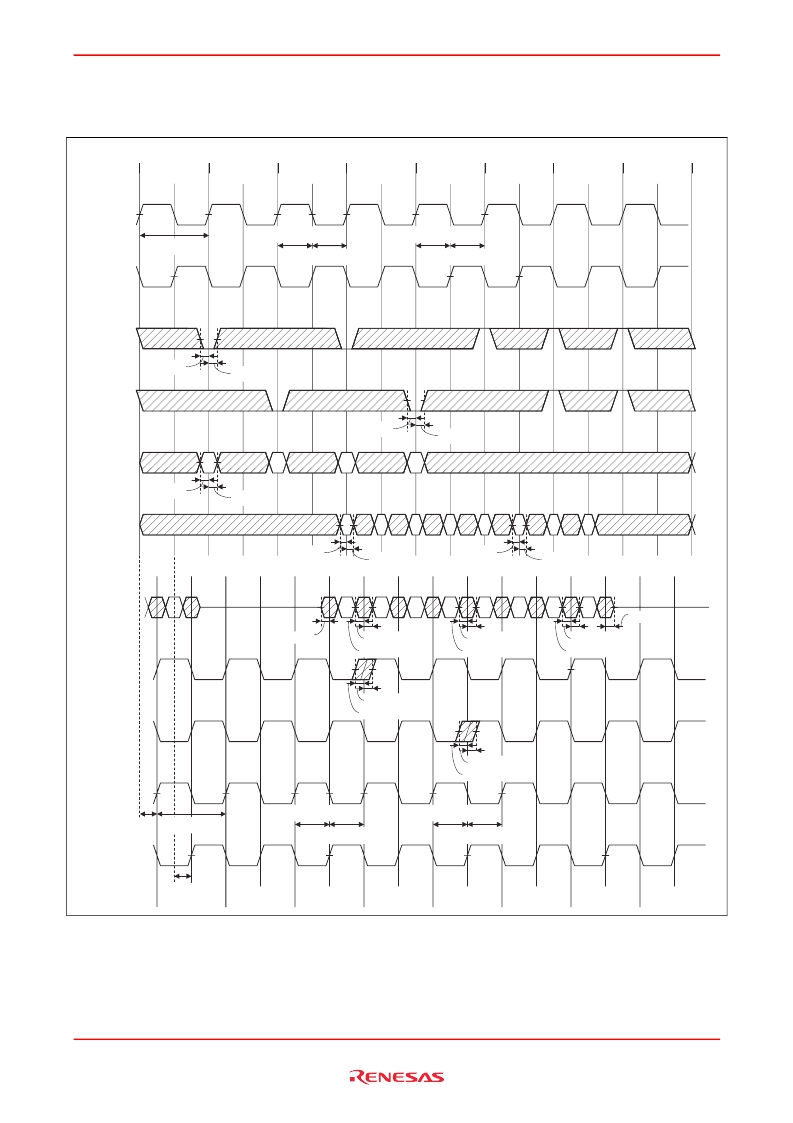

Timing Waveforms

Read and Write Timing

K

A0

D10

A1

A2

A3

D11

D12

D13

D30

D31

D32

D33

Q00

Qx3

Q01

Q02

Q03

Q20

Q21

Q22

Q23

NOP

READ

WRITE

READ

WRITE

NOP

NOP

NOP

tKHIX

tIVKH

tKHIX

tIVKH

tKHAX

tAVKH

tKHDX

tDVKH

tKHDX

tDVKH

/K

/R

/W

Address

Data in

tCHQV

-tCHQX

tCHQV

-tCHQX

tCQHQV

-tCQHQX

-tCHQX1

tCHQZ

tCHCQV

-tCHCQX

tCHCQV

-tCHCQX

tKHKH

tKHKL

tKLKH

tKH/KH

t/KHKH

tKHKH

tKHKL

tKLKH

tKH/KH

t/KHKH

tKHCH

tKHCH

Data out

CQ

/CQ

C

/C

1

2

3

4

5

6

7

8

9

Notes: 1. Q00 refers to output from address A0+0. Q01 refers to output from the next internal burst address following

A0, i.e., A0+1.

2. Outputs are disable (high-Z) one clock cycle after a NOP.

3. In this example, if address A2 = A1, then data Q20 = D10, Q21 = D11. Write data is forwarded immediately

as read results.

4. To control read and write operations, /BW signals must operate at the same timing as Data in.

REJ03C0295-0003 Rev.0.03 Jul. 31, 2007

Page 16 of 24

相关PDF资料 |

PDF描述 |

|---|---|

| R1Q3A3618 | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-30R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-33R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-40R | 36-Mbit QDR™II SRAM 4-word Burst |

| R1Q3A3618ABG-50R | 36-Mbit QDR™II SRAM 4-word Burst |

相关代理商/技术参数 |

参数描述 |

|---|---|

| R1Q3A3609ABG60RB0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3609ABG60RS0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3609ABG60RT0 | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 2-word Burst |

| R1Q3A3609BBG-33R | 制造商:Renesas Electronics Corporation 功能描述:SRAM Chip Sync Dual 1.8V 36M-Bit 4M x 9-Bit 0.45ns 165-Pin FBGA |

| R1Q3A3609BBG-40R | 制造商:RENESAS 制造商全称:Renesas Technology Corp 功能描述:36-Mbit QDR?II SRAM 4-word Burst |

发布紧急采购,3分钟左右您将得到回复。