- 您现在的位置:买卖IC网 > PDF目录69322 > RJ80530VY700256 (INTEL CORP) 32-BIT, 700 MHz, MICROPROCESSOR, PBGA479 PDF资料下载

参数资料

| 型号: | RJ80530VY700256 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 700 MHz, MICROPROCESSOR, PBGA479 |

| 封装: | MICRO, FCBGA-479 |

| 文件页数: | 8/101页 |

| 文件大小: | 2159K |

| 代理商: | RJ80530VY700256 |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页

Mobile Intel Celeron Processor Features

R

14

Mobile Intel

Celeron Processor (0.13 ) in

Micro-FCBGA and Micro-FCPGA Packages Datasheet

2.1.5

Signal Differences Between the Mobile Intel Celeron Processor

(0.18 ) (in BGA2 and Micro-PGA2 Packages) and the Mobile

Intel Celeron Processor (0.13 ) (in Micro-FCBGA and Micro-

FCPGA Packages)

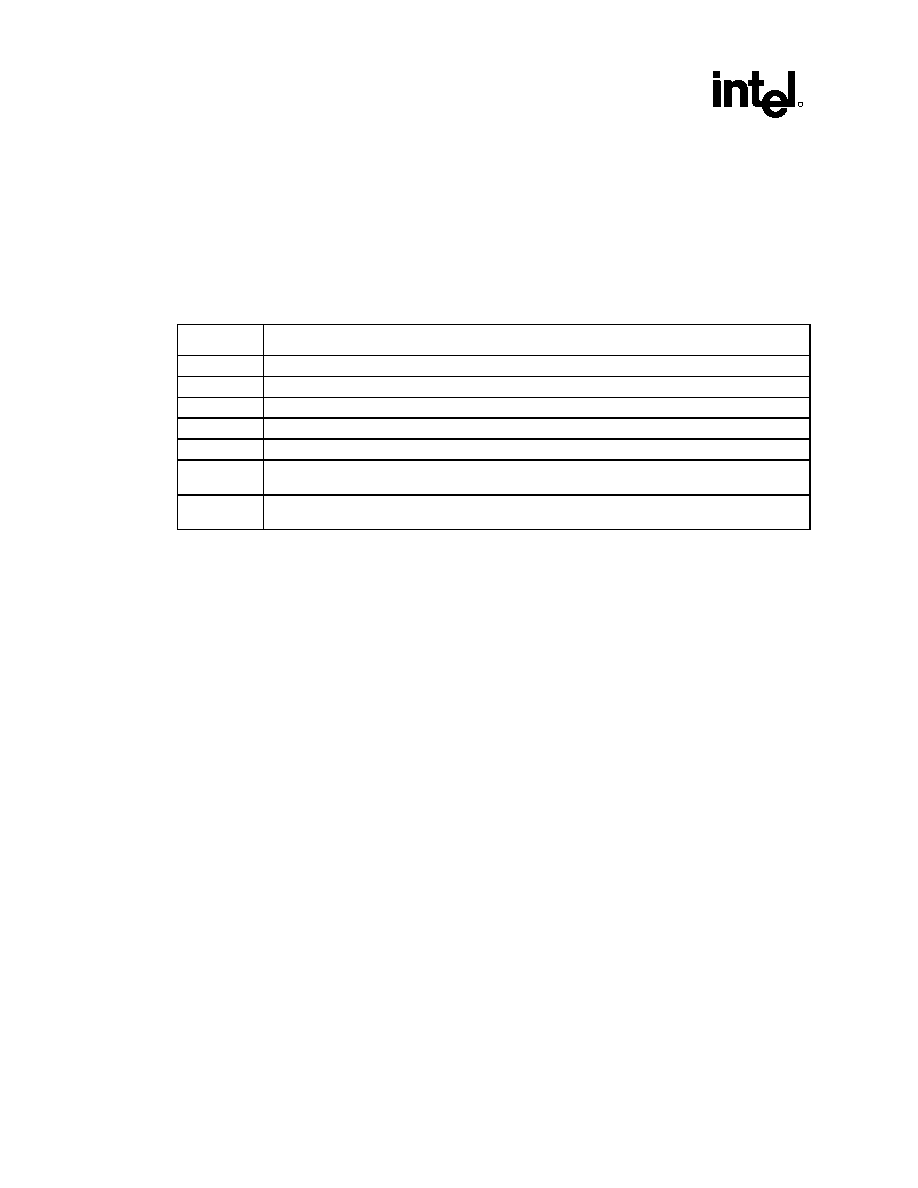

A list of new and changed signals is shown in Table 1.

Table 1. New and Revised Mobile Intel Celeron Processor (0.13 ) Signals

Signals

Function

BCLK, BCLK#

Differential host clk signals.

CLKREF

Host Clock reference signal in Single Ended Clocking mode.

BSEL[1:0]

Signals are output only instead of I/O. Please refer to the Appendix for details.

DPSLP#

Deep Sleep pin (replaces SLP# pin on the mobile Celeron processor (0.18 ))

NCTRL

AGTL output buffer pull down impedance control.

VID[4:0]

Voltage Identification (different implementation from mobile Celeron processor (0.18 )). Please refer

to Section 3.2.3 for details.

VTTPWRGD

Power Good signal for VCCT, which indicates that, the VID signals are stable. Please refer to Figure

3 for VTTPWRGD system level connections.

2.2

Power Management

2.2.1

Clock Control Architecture

The Mobile Intel Celeron Processor clock control architecture (Figure 1) has been optimized for leading

edge mobile computer designs. The clock control architecture consists of six different clock states:

Normal, Auto Halt, Quick Start, HALT/Grant Snoop and Deep Sleep states. The Auto Halt state

provides a low-power clock state that can be controlled through the software execution of the HLT

instruction. The Quick Start state provides a very low power and low exit latency clock state that can be

used for hardware controlled “idle” computer states. The Deep Sleep state provides extremely low-

power states that can be used for “Power-On-Suspend” computer states, which is an alternative to

shutting off the processor’s power. The exit latency of the Deep Sleep state is 30 msec in the Mobile

Intel Celeron Processor. Performing state transitions not shown in Figure 1 is neither recommended nor

supported. Figure 2 provides the clock state characteristics, which are described in detail in the following

sections.

2.2.2

Normal State

The Normal state of the processor is the normal operating mode where the processor’s core clock is

running and the processor is actively executing instructions.

2.2.3

Auto Halt State

This is a low-power mode entered by the processor through the execution of the HLT instruction. A

transition to the Normal state is made by a halt break event (one of the following signals going active:

NMI, INTR, BINIT#, INIT#, RESET#, FLUSH#, or SMI#).

相关PDF资料 |

PDF描述 |

|---|---|

| RH80530WZ014256 | 32-BIT, 1333 MHz, MICROPROCESSOR, CPGA478 |

| RH80532NC021256 | 32-BIT, 1500 MHz, MICROPROCESSOR, CPGA478 |

| RH80532GC025512 | 32-BIT, 1600 MHz, MICROPROCESSOR, CPGA478 |

| RH80532GC021512 | 32-BIT, 1500 MHz, MICROPROCESSOR, CPGA478 |

| RH80532GC017512 | 32-BIT, 1400 MHz, MICROPROCESSOR, CPGA478 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RJ80530VY800256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530VZ800256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80535GC0171M | 制造商:Rochester Electronics LLC 功能描述:MOBILE PENTIUM M,1.4GHZ,1M,UFCBGA - Bulk 制造商:Intel 功能描述: |

| RJ80535GC0171M S L6F5 | 制造商:Intel 功能描述:MPU Pentium? M Processor RISC 32-Bit 130nm 1.4GHz 479-Pin HPBGA Tray 制造商:Intel 功能描述:PENTIUM M PROCESSOR 1.40 GHZ |

| RJ80535GC0211M | 制造商:Intel 功能描述: |

发布紧急采购,3分钟左右您将得到回复。