- 您现在的位置:买卖IC网 > PDF目录69322 > RJ80530VY700256 (INTEL CORP) 32-BIT, 700 MHz, MICROPROCESSOR, PBGA479 PDF资料下载

参数资料

| 型号: | RJ80530VY700256 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 700 MHz, MICROPROCESSOR, PBGA479 |

| 封装: | MICRO, FCBGA-479 |

| 文件页数: | 9/101页 |

| 文件大小: | 2159K |

| 代理商: | RJ80530VY700256 |

第1页第2页第3页第4页第5页第6页第7页第8页当前第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页

Mobile Intel Celeron Processor Features

R

Mobile Intel

Celeron Processor (0.13 ) in

15

Micro-FCBGA and Micro-FCPGA Packages Datasheet

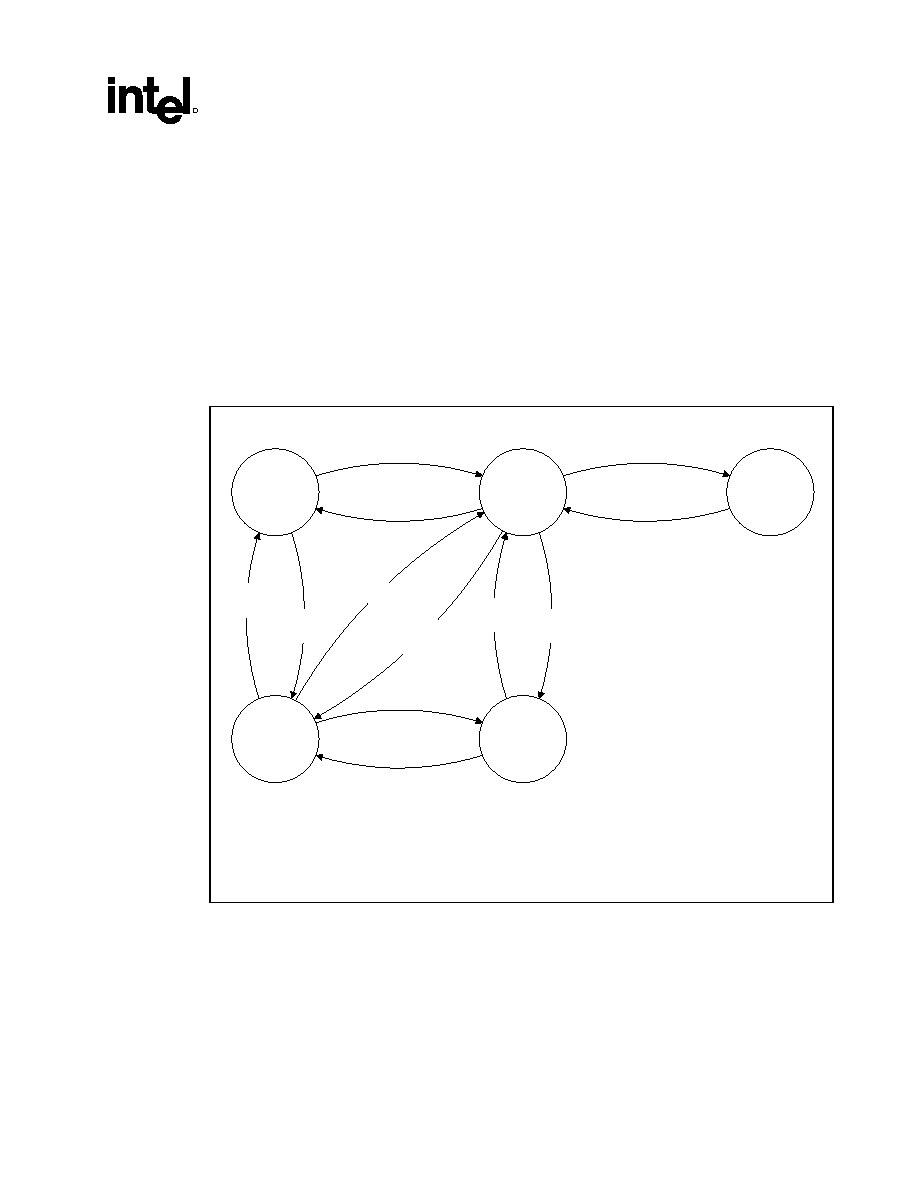

Asserting the STPCLK# signal while in the Auto Halt state will cause the processor to transition to the

Quick Start state. Deasserting STPCLK# will cause the processor to return to the Auto Halt state

without issuing a new Halt bus cycle.

The SMI# interrupt is recognized in the Auto Halt state. The return from the System Management

Interrupt (SMI) handler can be to either the Normal state or the Auto Halt state. See the Intel

Architecture Software Developer’s Manual, Volume III: System Programmer’s Guide for more

information. No Halt bus cycle is issued when returning to the Auto Halt state from the System

Management Mode (SMM).

The FLUSH# signal is serviced in the Auto Halt state. After the on-chip and off-chip caches have been

flushed, the processor will return to the Auto Halt state without issuing a Halt bus cycle. Transitions in

the A20M# and PREQ# signals are recognized while in the Auto Halt state.

Figure 1. Clock Control States

Quick Start

Normal

HS=false

Deep Sleep 2

HALT/Grant

Snoop

Auto Halt

HS=true

STPCLK#1

BCLK stopped

or DPSLP#

snoop

occurs

BCLK on

and !DPSLP#

(!STPCLK# and !HS)

or RESET#

snoop

serviced

HLT

instruction1

snoop

serviced

snoop

occurs

STPCLK#1

!STPCLK#

and HS

halt

break

V0001-022

NOTES:

1. State transition does not occur until the Stop Grant or Auto Halt acknowledge bus cycle completes

Halt break – A20M#, BINIT#, FLUSH#, INIT#, INTR, NMI, PREQ#, RESET#, SMI#, or APIC interrupt

HLT – HLT instruction executed

HS – Processor Halt State

2. Restrictions apply to the use of both methods of entering Deep Sleep. See Deep Sleep state description for details.

2.2.4

Quick Start State

The processor is required to be configured for the Quick Start state by strapping the A15# signal low. In

the Quick Start state the processor is only capable of acting on snoop transactions generated by the

system bus priority device. Because of its snooping behavior, Quick Start can only be used in a

uniprocessor (UP) configuration.

相关PDF资料 |

PDF描述 |

|---|---|

| RH80530WZ014256 | 32-BIT, 1333 MHz, MICROPROCESSOR, CPGA478 |

| RH80532NC021256 | 32-BIT, 1500 MHz, MICROPROCESSOR, CPGA478 |

| RH80532GC025512 | 32-BIT, 1600 MHz, MICROPROCESSOR, CPGA478 |

| RH80532GC021512 | 32-BIT, 1500 MHz, MICROPROCESSOR, CPGA478 |

| RH80532GC017512 | 32-BIT, 1400 MHz, MICROPROCESSOR, CPGA478 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RJ80530VY800256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80530VZ800256 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| RJ80535GC0171M | 制造商:Rochester Electronics LLC 功能描述:MOBILE PENTIUM M,1.4GHZ,1M,UFCBGA - Bulk 制造商:Intel 功能描述: |

| RJ80535GC0171M S L6F5 | 制造商:Intel 功能描述:MPU Pentium? M Processor RISC 32-Bit 130nm 1.4GHz 479-Pin HPBGA Tray 制造商:Intel 功能描述:PENTIUM M PROCESSOR 1.40 GHZ |

| RJ80535GC0211M | 制造商:Intel 功能描述: |

发布紧急采购,3分钟左右您将得到回复。