- 您现在的位置:买卖IC网 > PDF目录69323 > RN80532KC041512 (INTEL CORP) 32-BIT, 2000 MHz, MICROPROCESSOR, CPGA603 PDF资料下载

参数资料

| 型号: | RN80532KC041512 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 2000 MHz, MICROPROCESSOR, CPGA603 |

| 封装: | Interposer, Micro, PGA-603 |

| 文件页数: | 70/129页 |

| 文件大小: | 1640K |

| 代理商: | RN80532KC041512 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页第60页第61页第62页第63页第64页第65页第66页第67页第68页第69页当前第70页第71页第72页第73页第74页第75页第76页第77页第78页第79页第80页第81页第82页第83页第84页第85页第86页第87页第88页第89页第90页第91页第92页第93页第94页第95页第96页第97页第98页第99页第100页第101页第102页第103页第104页第105页第106页第107页第108页第109页第110页第111页第112页第113页第114页第115页第116页第117页第118页第119页第120页第121页第122页第123页第124页第125页第126页第127页第128页第129页

Intel Xeon Processor with 512 KB L2 Cache

Datasheet

45

3.0

Front Side Bus Signal Quality Specifications

This section documents signal quality metrics used to derive topology and routing guidelines

through simulation. All specifications are made at the processor core (pad measurements).

Source synchronous data transfer requires the clean reception of data signals and their associated

strobes. Ringing below receiver thresholds, non-monotonic signal edges, and excessive voltage

swing will adversely affect system timings. Ringback and signal non-monotinicity cannot be

tolerated since these phenomena may inadvertently advance receiver state machines. Excessive

signal swings (overshoot and undershoot) are detrimental to silicon gate oxide integrity, and can

cause device failure if absolute voltage limits are exceeded. Additionally, overshoot and

undershoot can degrade timing due to the build up of inter-symbol interference (ISI) effects. For

these reasons, it is crucial that the designer assure acceptable signal quality across all systematic

variations encountered in volume manufacturing.

Specifications for signal quality are for measurements at the processor core only and are only

observable through simulation. The same is true for all front side bus AC timing specifications in

Section 2.13. Therefore, proper simulation of the processor front side bus is the only means to

verify proper timing and signal quality metrics.

3.1

Front Side Bus Clock (BCLK) Signal Quality Specifications

and Measurement Guidelines

Table 21 describes the signal quality specifications at the processor pads for the processor front

side bus clock (BCLK) signals. Figure 20 describes the signal quality waveform for the front side

bus clock at the processor pads.

NOTES:

1. Unless otherwise noted, all specifications in this table apply to all processor frequencies and cache sizes.

2. The rising and falling edge ringback voltage specified is the minimum (rising) or maximum (falling) absolute

voltage the BCLK signal can dip back to after passing the V

IH (rising) or VIL (falling) voltage limits. This

specification is an absolute value.

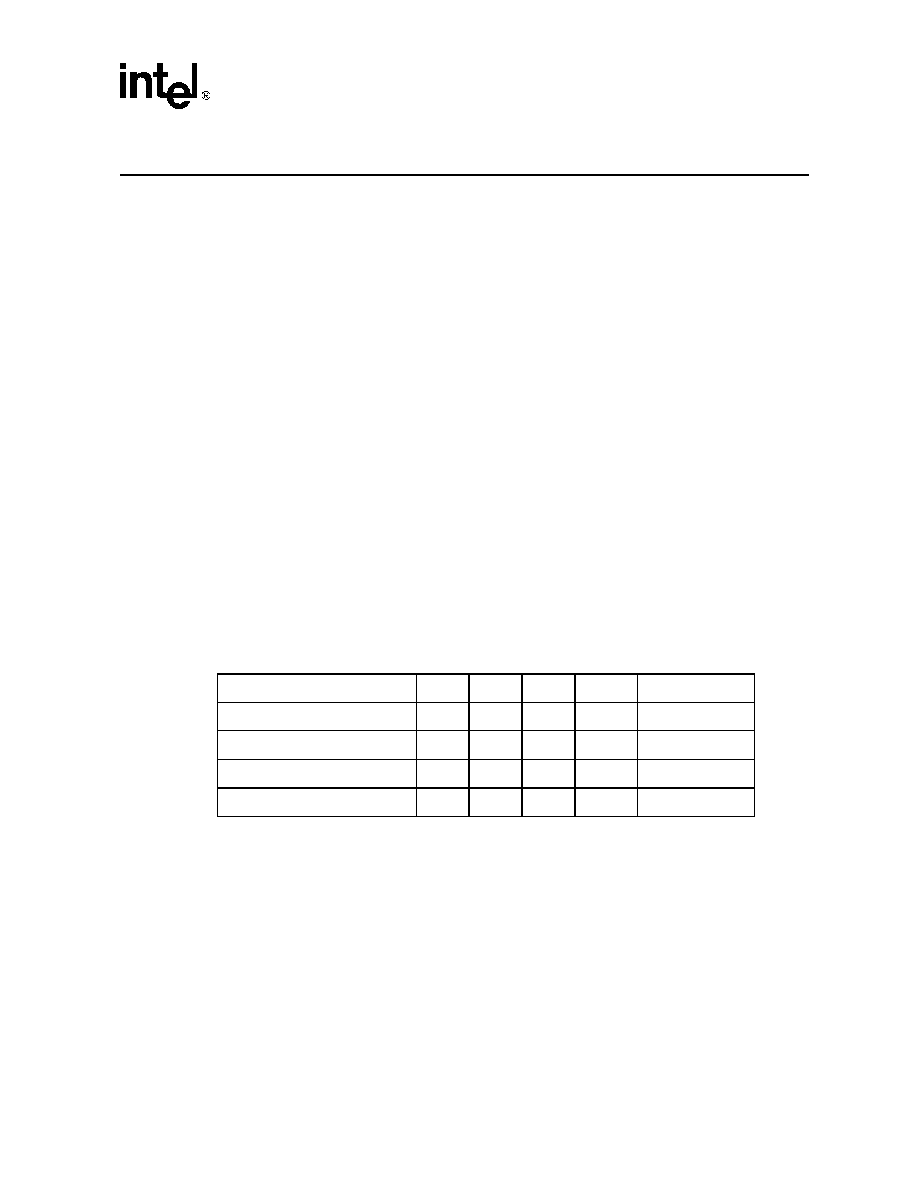

Table 21. BCLK Signal Quality Specifications

Parameter

Min

Max

Unit

Figure

Notes

BCLK[1:0] Overshoot

N/A

0.30

V

1

BCLK[1:0] Undershoot

N/A

0.30

V

1

BCLK[1:0] Ringback Margin

0.20

N/A

V

1

BCLK[1:0] Threshold Region

N/A

0.10

V

1, 2

相关PDF资料 |

PDF描述 |

|---|---|

| RP0352 | GRAPHICS PROCESSOR, PQFP80 |

| RP65C02G-06 | 8-BIT, 6 MHz, MICROPROCESSOR, PDIP40 |

| RPIXP2800BC | 32-BIT, 650 MHz, RISC PROCESSOR, PBGA1356 |

| RPIXP2850BB | 32-BIT, 1400 MHz, RISC PROCESSOR, PBGA1356 |

| RPM-075PTT86 | PHOTO TRANSISTOR DETECTOR |

相关代理商/技术参数 |

参数描述 |

|---|---|

| RN80532KC041512 SL5Z9 | 制造商:Intel 功能描述:MPU XEON 0.13UM 2GHZ 603-PIN UFCBGA - Trays |

| RN80532KC041512 SL6EM | 制造商:Intel 功能描述:MPU XEON 0.13UM 2GHZ 603-PIN UFCBGA - Trays |

| RN80532KC041512S L5Z9 | 制造商:Intel 功能描述:MPU Xeon? Processor 0.13um 2GHz 603-Pin uFCBGA |

| RN80532KC041512S L6W6 | 制造商:Intel 功能描述:MPU Xeon? Processor 0.13um 2GHz 603-Pin uFCBGA |

| RN80532KC041512SL6EM | 功能描述:IC MPU XEON 1.5V 2.0GHZ 603-INT3 RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

发布紧急采购,3分钟左右您将得到回复。