- 您现在的位置:买卖IC网 > PDF目录98071 > S80960SB-10 (INTEL CORP) 32-BIT, 10 MHz, RISC PROCESSOR, PQFP80 PDF资料下载

参数资料

| 型号: | S80960SB-10 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 32-BIT, 10 MHz, RISC PROCESSOR, PQFP80 |

| 封装: | EIAJ, QFP-80 |

| 文件页数: | 6/38页 |

| 文件大小: | 1870K |

| 代理商: | S80960SB-10 |

第1页第2页第3页第4页第5页当前第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页

10

80960SB

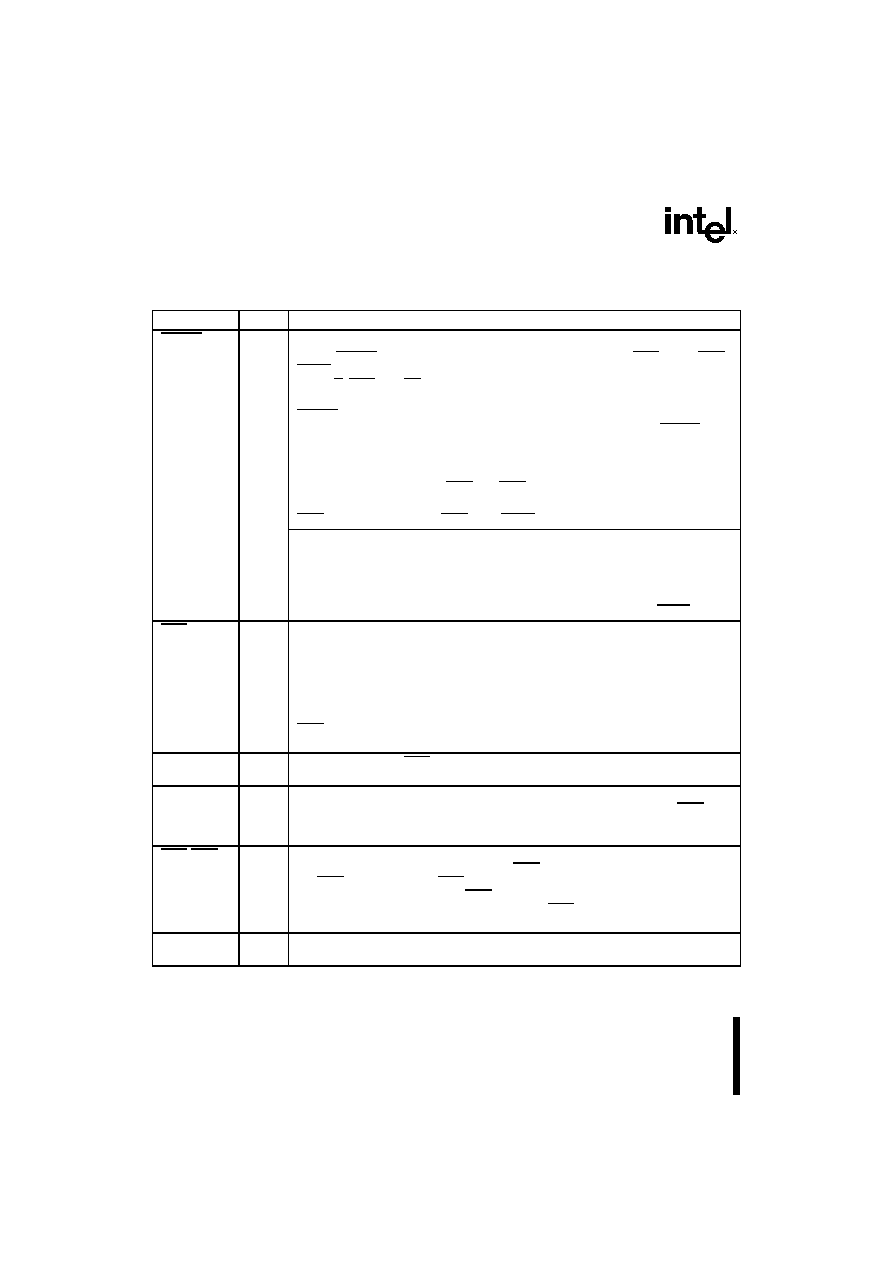

Table 5. 80960SB Pin Description: Support Signals

NAME

TYPE

DESCRIPTION

RESET

I

RESET clears the processor’s internal logic and causes it to reinitialize.

During RESET assertion, the input pins are ignored (except for INT0, INT1, INT3,

LOCK), the three-state output pins are placed in a HIGH impedance state (except

for DT/R, DEN, and AS) and other output pins are placed in their non-asserted

states.

RESET must be asserted for at least 41 CLK2 cycles for a predictable reset.

Optionally, for a synchronous reset, the LOW and HIGH transition of RESET

should occur after the rising edge of both CLK2 and the external bus CLK and

before the next rising edge of CLK2.

The interrupt pins indicate the initialization sequence executed. Typical initial-

ization requires driving only INT0 and INT3 to a HIGH state. The reset conditions

follow:

INT0

INT1

INT3

LOCK

Action Taken

1

x

1

Run self test (core initialization)

0

1

Disable self-test

0

1

x

Reserved

x

0

x

Reserved

x

0

ONCE mode (see LOCK pin)

INT0

I

INTERRUPT 0 indicates a pending interrupt. To signal an interrupt in a

synchronous system, this pin — as well as the other interrupt pins — must be

enabled by being deasserted for at least one bus cycle and then asserted for at

least one additional bus cycle. In an asynchronous system, the pin must remain

deasserted for at least two system clock cycles and then asserted for at least two

more system clock cycles. The interrupt control register must be programmed with

an interrupt vector before using this pin.

INT0 is sampled during reset to determine if the self-test sequence is to be

executed.

INT1

I

INTERRUPT 1, like INT0, provides direct interrupt signaling. INT1 is sampled

during reset to determine if the self-test sequence is to be executed.

INT2/INTR

I

INTERRUPT2/INTERRUPT REQUEST: The interrupt control register determines

how this pin is interpreted. If INT2, it has the same interpretation as the INT0 and

INT1 pins. If INTR, it is used to receive an interrupt request from an external

interrupt controller.

INT3/INTA

I/O

T.S.

INTERRUPT3/INTERRUPT ACKNOWLEDGE: The interrupt control register

determines how this pin is interpreted. If INT3, it has the same interpretation as

the INT0 and INT1 pins. If INTA, it is used as an output to control interrupt

acknowledge transactions. The INTA output is latched on-chip and remains valid

during Td cycles; as an output, it is open-drain. INT3 must be pulled HIGH during

reset.

NC

N/A

NOT CONNECTED indicates pins should not be connected. Never connect any

pin marked NC; these pins may be reserved for factory use.

I/O = Input/Output, O = Output, I = Input, O.D. = Open Drain, T.S. = Three-state

相关PDF资料 |

PDF描述 |

|---|---|

| S80C186XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80C186XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| S80C188XL20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| S80C188XL12 | 16-BIT, 12 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S80960SB-16 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:EMBEDDED 32-BIT MICROPROCESSOR WITH 16-BIT BURST DATA BUS |

| S80BH97(E)4-C WAF | 制造商:Intel 功能描述: |

| S80C154-12 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| S80C154-16 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

| S80C154-20 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:8-Bit Microcontroller |

发布紧急采购,3分钟左右您将得到回复。