- 您现在的位置:买卖IC网 > PDF目录69327 > S80C188EB-13 (INTEL CORP) 16-BIT, 13 MHz, MICROPROCESSOR, PQFP80 PDF资料下载

参数资料

| 型号: | S80C188EB-13 |

| 厂商: | INTEL CORP |

| 元件分类: | 微控制器/微处理器 |

| 英文描述: | 16-BIT, 13 MHz, MICROPROCESSOR, PQFP80 |

| 封装: | EIAJ, QFP-80 |

| 文件页数: | 4/59页 |

| 文件大小: | 1928K |

| 代理商: | S80C188EB-13 |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页第33页第34页第35页第36页第37页第38页第39页第40页第41页第42页第43页第44页第45页第46页第47页第48页第49页第50页第51页第52页第53页第54页第55页第56页第57页第58页第59页

80C186EB80C188EB 80L186EB80L188EB

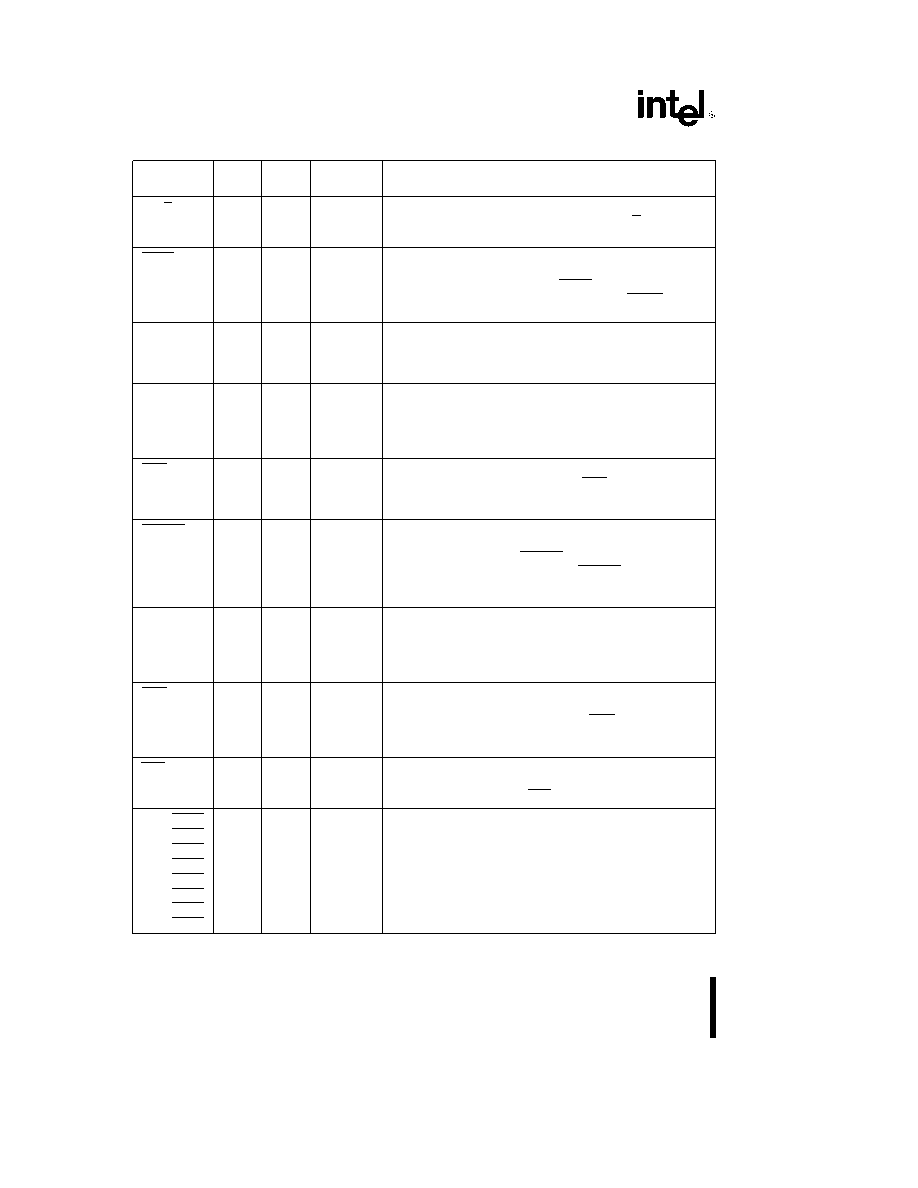

Table 3 Pin Descriptions

(Continued)

Pin

Input

Output

Description

Name

Type

States

DTR

O

H(Z)

Data TransmitReceive

output controls the direction of a

bi-directional buffer in a buffered system DTR is only

R(Z)

available for the PLCC package

P(X)

LOCK

O

H(Z)

LOCK

output indicates that the bus cycle in progress is not

to be interrupted The processor will not service other bus

R(WH)

requests (such as HOLD) while LOCK is active This pin is

P(1)

configured as a weakly held high input while RESIN is

active and must not be driven low

HOLD

I

A(L)

HOLD

request input to signal that an external bus master

wishes to gain control of the local bus The processor will

relinquish control of the local bus between instruction

boundaries not conditioned by a LOCK prefix

HLDA

O

H(1)

HoLD Acknowledge

output to indicate that the processor

has relinquished control of the local bus When HLDA is

R(0)

asserted the processor will (or has) floated its data bus

P(0)

and control signals allowing another bus master to drive the

signals directly

NCS

O

H(1)

Numerics Coprocessor Select

output is generated when

accessing a numerics coprocessor NCS is not provided on

(NC)

R(1)

the QFP or SQFP packages This signal does not exist on

P(1)

the 80C188EB80L188EB

ERROR

I

A(L)

ERROR

input that indicates the last numerics coprocessor

operation resulted in an exception condition An interrupt

(NC)

TYPE 16 is generated if ERROR is sampled active at the

beginning of a numerics operation ERROR is not provided

on the QFP or SQFP packages This signal does not exist

on the 80C188EB80L188EB

PEREQ

I

A(L)

CoProcessor REQuest

signals that a data transfer

between an External Numerics Coprocessor and Memory is

(NC)

pending PEREQ is not provided on the QFP or SQFP

packages This signal does not exist on the 80C188EB

80L188EB

UCS

O

H(1)

Upper Chip Select

will go active whenever the address of

a memory or IO bus cycle is within the address limitations

R(1)

programmed by the user After reset UCS is configured to

P(1)

be active for memory accesses between 0FFC00H and

0FFFFFH

LCS

O

H(1)

Lower Chip Select

will go active whenever the address of

a memory bus cycle is within the address limitations

R(1)

programmed by the user LCS is inactive after a reset

P(1)

P10GCS0

O

H(X)H(1)

These pins provide a multiplexed function If enabled each

pin can provide a Generic Chip Select output which will go

P11GCS1

R(1)

active whenever the address of a memory or IO bus cycle

P12GCS2

P(X)P(1)

is within the address limitations programmed by the user

P13GCS3

When not programmed as a Chip-Select each pin may be

P14GCS4

used as a general purpose output Port As an output port

P15GCS5

pin the value of the pin can be read internally

P16GCS6

P17GCS7

NOTE

Pin names in parentheses apply to the 80C188EB80L188EB

12

相关PDF资料 |

PDF描述 |

|---|---|

| S80C188EB-20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| SB80C188EB-20 | 16-BIT, 20 MHz, MICROPROCESSOR, PQFP80 |

| SB80C188EB-25 | 16-BIT, 25 MHz, MICROPROCESSOR, PQFP80 |

| S80L186EB-13 | 16-BIT, 13 MHz, MICROPROCESSOR, PQFP80 |

| SB80L188EB-13 | 16-BIT, 13 MHz, MICROPROCESSOR, PQFP80 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| S80C188EB20 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| S80C188EB25 | 功能描述:IC MPU 16-BIT 5V 25MHZ 80-MQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微处理器 系列:- 标准包装:2 系列:MPC8xx 处理器类型:32-位 MPC8xx PowerQUICC 特点:- 速度:133MHz 电压:3.3V 安装类型:表面贴装 封装/外壳:357-BBGA 供应商设备封装:357-PBGA(25x25) 包装:托盘 |

| S80C188EB-25 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Microprocessor |

| S80C188EC13 | 制造商:INTEL 制造商全称:Intel Corporation 功能描述:16-BIT HIGH-INTEGRATION EMBEDDED PROCESSORS |

| S80C188EC-13 | 制造商:未知厂家 制造商全称:未知厂家 功能描述:16-Bit Microprocessor |

发布紧急采购,3分钟左右您将得到回复。