- 您现在的位置:买卖IC网 > PDF目录225181 > SIW3500GIG3 (RF MICRO DEVICES INC) SPECIALTY TELECOM CIRCUIT, PBGA96 PDF资料下载

参数资料

| 型号: | SIW3500GIG3 |

| 厂商: | RF MICRO DEVICES INC |

| 元件分类: | 通信及网络 |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PBGA96 |

| 封装: | 6 X 6 MM, GREEN, VFBGA-96 |

| 文件页数: | 24/28页 |

| 文件大小: | 795K |

| 代理商: | SIW3500GIG3 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页当前第24页第25页第26页第27页第28页

Preliminary

5 of 28

SiW3500

60 0066 R00JIrf SiW3500 UltimateBlue SoC DS

Low Power Clock

For the Bluetooth low power clock, a 32.768-kHz crystal can be used to drive the SiW3500 oscillator circuit, or alterna-

tively, a 32.768-kHz reference clock signal can be used instead of a crystal. If the lowest power consumption is not

required during low-power modes such as sniff, hold, park, and idle modes, the 32.768-kHz crystal may be omitted in the

design. If the 32.768-kHz clock source is used, the clock source should be connected to the CLK32_IN pin via an AC-

coupling capacitor (100 pF or greater), and its amplitude must meet the following requirements:

For AC-coupled via 100 pF or greater (peak-to-peak voltage):

400 mVP-P < CLK32_IN < VDD_C

Note:

Note: It is recommended to keep CLK32_IN voltage to 1 Vp-p maximum to minimize the I/O power supply current when the

VBATT_ANA and VBATT_DIG are shut off while VDD_P and VDD_P_ALT are still powered. The CLK32_OUT can be left open.

However, connecting the CLK32_OUT pin to either VDD_P or GND through a 100 nF capacitor improves the circuit's sensitivity

slightly if operating near the low end of the CLK32_IN range above.

Power Supply Description

The SiW3500 operates at 1.8 V core voltage for internal analog and digital circuits. The chip has internal analog and

digital voltage regulators simplifying power supply requirements to the chip. The internal voltage regulators can be

supplied directly from a battery or from other system voltage sources. Optionally, the internal regulators can be by-

passed if a 1.8 V regulated source is available on the system.

Note:

Both regulators can be bypassed if external regulation is desired. When bypassing the analog regulator, the VBATT_ANA and

VCC_OUT pins must be tied together and the external analog voltage (1.8 V) should be applied to the VBATT_ANA pin. When

bypassing the digital regulator, the VBATT_DIG pin should be left unconnected and the external digital voltage (1.8 V) should be

applied to VDD_C pin.

The power for the I/Os is taken from two separate sources (VDD_P and VDD_P_ALT). They can range from 1.62 to 3.63

Volts to maintain compatibility with a wide range of peripheral devices. Please check the pin list for the exact pins that are

powered from the VDD_P and VDD_P_ALT sources.

RF I/O Description

The SiW3500 employs single-ended RF input and output pins for reduced external components. In typical power class 2

(0 dBm nominal) applications, no external matching components are necessary.

On-Chip Memory

The SiW3500 SoC integrates both SRAM and ROM. The ROM is pre-programmed with Bluetooth protocol stack

software (HCI software) and boot code that executes automatically upon reset. The boot code serves to control the boot

sequence as well as to direct the execution to the appropriate memory for continued operation.

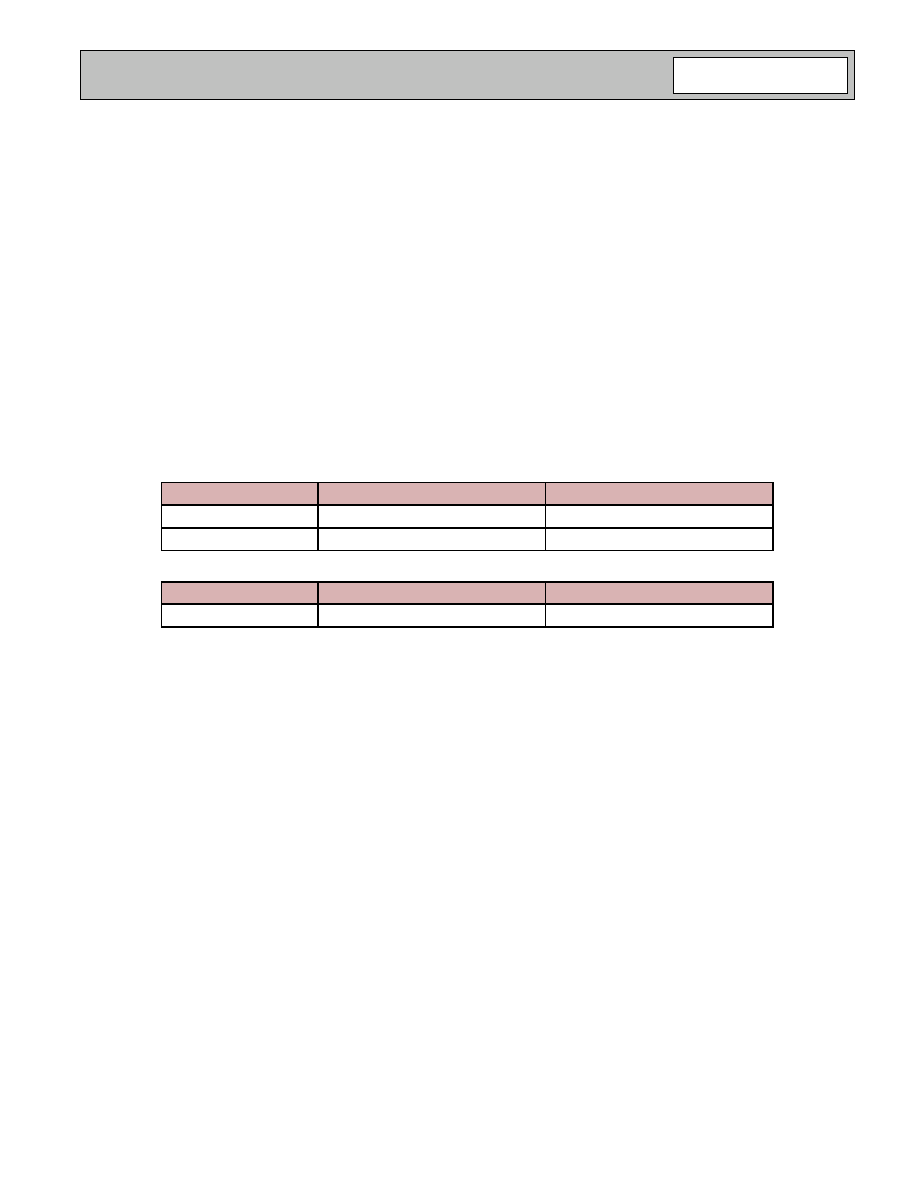

Function

Internal Analog Regulator

Internal Digital Regulator

Regulator input pin

VBATT_ANA = 2.3 to 3.63 V

VBATT_DIG = 2.3 to 3.63 V

Regulator output pin

VCC_OUT = 1.8 V

VDD_C = 1.8 V

Internal Regulator Used

Function

Analog Core Circuits

Digital Core Circuits

Circuit voltage supply pin

VCC = 1.8 V

VDD_C = 1.8 V

Internal Regulator Bypassed

相关PDF资料 |

PDF描述 |

|---|---|

| SJ6620 | 2 A, SILICON, RECTIFIER DIODE |

| SJG020100 | SJG12, RELAY SOCKET |

| SJL-117 | 2 MHz - 200 MHz RF/MICROWAVE 180 DEGREE HYBRID COUPLER, 1.3 dB INSERTION LOSS-MAX |

| SK1812L-AE3-4-R | BIPOLAR LATCH TYPE HALL - EFFECT FOR HIGH-TEMPERATURE OPERATION |

| SK1812L-G03-D-K | BIPOLAR LATCH TYPE HALL - EFFECT FOR HIGH-TEMPERATURE OPERATION |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SIW73 | 制造商:DELTA 制造商全称:Delta Electronics, Inc. 功能描述:SMT Power Inductor |

| SIW73-100 | 制造商:DELTA 制造商全称:Delta Electronics, Inc. 功能描述:SMT Power Inductor |

| SIW73-101 | 制造商:DELTA 制造商全称:Delta Electronics, Inc. 功能描述:SMT Power Inductor |

| SIW73-120 | 制造商:DELTA 制造商全称:Delta Electronics, Inc. 功能描述:SMT Power Inductor |

| SIW73-150 | 制造商:DELTA 制造商全称:Delta Electronics, Inc. 功能描述:SMT Power Inductor |

发布紧急采购,3分钟左右您将得到回复。