- 您现在的位置:买卖IC网 > PDF目录297406 > SL811HS-JCT (CYPRESS SEMICONDUCTOR CORP) UNIVERSAL SERIAL BUS CONTROLLER, PQCC28 PDF资料下载

参数资料

| 型号: | SL811HS-JCT |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQCC28 |

| 封装: | LEAD FREE, PLASTIC, LCC-28 |

| 文件页数: | 4/32页 |

| 文件大小: | 854K |

| 代理商: | SL811HS-JCT |

第1页第2页第3页当前第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

SL811HS

Document 38-08008 Rev. *D

Page 12 of 32

SL811HS Slave Mode Registers

When in slave mode, the registers in the SL811HS are divided

into two major groups. The first group contains Endpoint reg-

isters that manage USB control transactions and data flow.

The second group contains the USB Registers that provide the

control and status information for all other operations.

Endpoint Registers

Communication and data flow on USB is implemented using

endpoints. These uniquely identifiable entities are the

terminals of communication flow between a USB host and

USB devices. Each USB device is composed of a collection of

independently operating endpoints. Each endpoint has a

unique identifier, which is the Endpoint Number. For more

information, see USB Specification 1.1 section 5.3.1.

The SL811HS supports four endpoints numbered 0–3.

Endpoint 0 is the default pipe and is used to initialize and

generically manipulate the device to configure the logical

device as the Default Control Pipe. It also provides access to

the device's configuration information, allows USB status and

control access, and supports control transfers.

Endpoints 1–3 support Bulk, Isochronous, and Interrupt

transfers. Endpoint 3 is supported by DMA. Each endpoint has

two sets of registers—the 'A' set and the 'B' set. This allows

overlapped operation where one set of parameters is set up

and the other is transferring. Upon completion of a transfer to

an endpoint, the ‘next data set’ bit indicates whether set 'A' or

set 'B' is used next. The ‘armed’ bit of the next data set

indicates whether the SL811HS is ready for the next transfer

without interruption.

Endpoints 0–3 Register Addresses

Each endpoint set has a group of five registers that are

mapped within the SL811HS memory. The register sets have

address assignments as shown in the following table.

For each endpoint set (starting at address Index = 0), the

registers are mapped as shown in the following table.

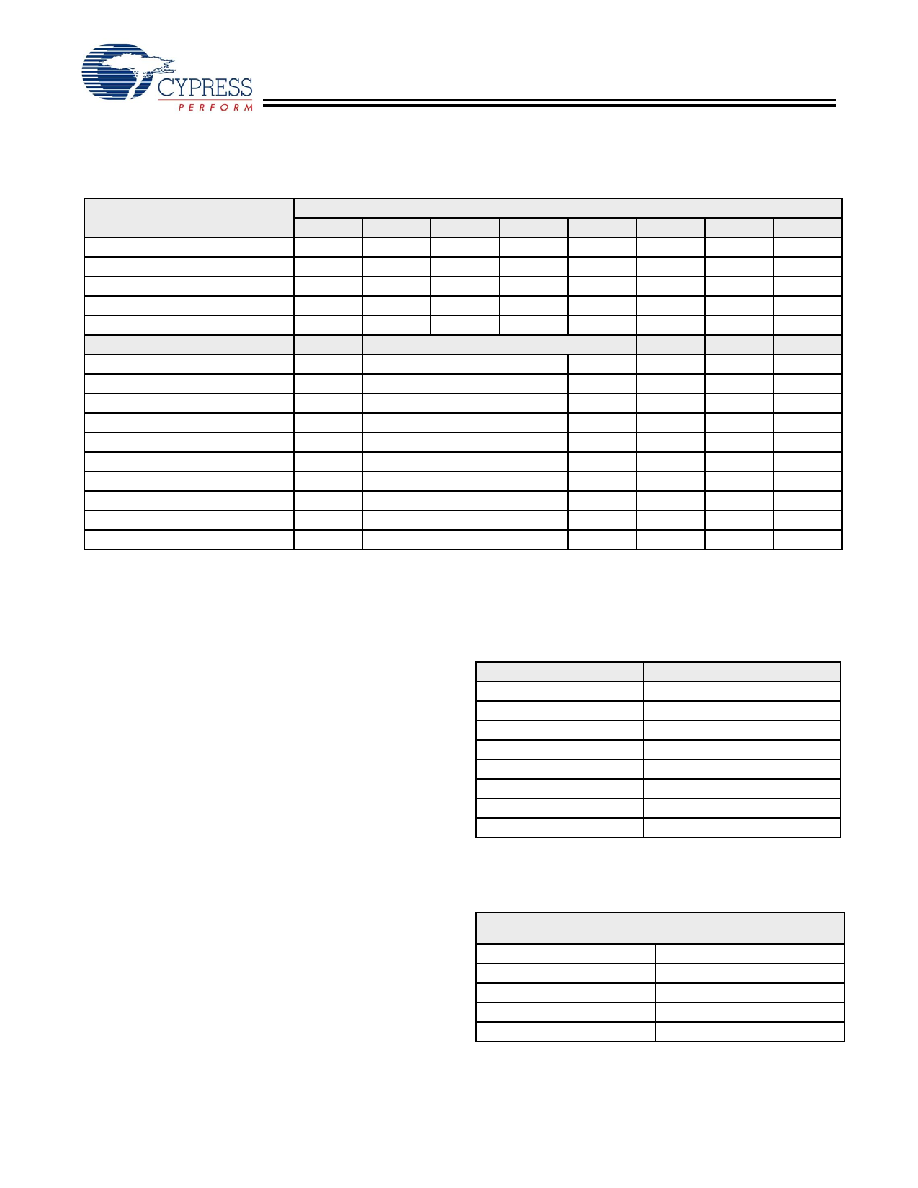

Table 19. SL811HS Slave/Peripheral Mode Register Summary

Register Name

Endpoint specific register addresses

EP 0 – A EP 0 - B

EP 1 – A

EP 1 - B

EP 2 - A

EP 2 - B EP 3 - A

EP 3 - B

EP Control Register

00h

08h

10h

18h

20h

28h

30h

0x38

EP Base Address Register

01h

09h

11h

19h

21h

29h

31h

0x39

EP Base Length Register

02h

0Ah

12h

1Ah

22h

2Ah

0x32

0x3A

EP Packet Status Register

03h

0Bh

13h

1Bh

23h

2Bh

0x33

0x3B

EP Transfer Count Register

04h

0Ch

14h

1Ch

24h

2Ch

0x34

0x3C

Register Name

Miscellaneous register addresses

Control Register 1

05h

Interrupt Status Register

0Dh

Interrupt Enable Register

06h

Current Data Set Register

0Eh

USB Address Register

07h

Control Register 2

0Fh

SOF Low Register (read only)

15h

Reserved

1Dh1Fh

SOF High Register (read only)

16h

Reserved

25h-27h

Reserved

17h

Reserved

2Dh-2Fh

DMA Total Count Low Register

35h

DMA Total Count High Register

36h

Reserved

37h

Memory Buffer

40h – FFh

Table 20. Endpoints 0–3 Register Addresses

Endpoint Register Set

Address (in Hex)

Endpoint 0 – a

00 - 04

Endpoint 0 – b

08 - 0C

Endpoint 1 – a

10 - 14

Endpoint 1 – b

18 - 1C

Endpoint 2 – a

20 - 24

Endpoint 2 – b

28 - 2C

Endpoint 3 – a

30 - 34

Endpoint 3 – b

38 - 3C

Table 21. Register Address Map

Endpoint Register Sets

(for Endpoint n starting at register position Index=0)

Index

Endpoint n Control

Index + 1

Endpoint n Base Address

Index + 2

Endpoint n Base Length

Index + 3

Endpoint n Packet Status

Index + 4

Endpoint n Transfer Count

相关PDF资料 |

PDF描述 |

|---|---|

| SL811HS | SL811HS Embedded USB Host/Slave Controller(SL811HS嵌入式USB主/从控制器) |

| SLA0201 | 600 V, SCR |

| SLA24C01-D-3/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLA24C01-D/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLE24C01-S/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SL811HST | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

| SL811HST-1.5 | 制造商:Cypress Semiconductor 功能描述:BUS Controller Circuit, 48 Pin, QFP |

| SL811HST-AC | 功能描述:IC USB HOST/SLAVE CTRLR 48LQFP RoHS:否 类别:集成电路 (IC) >> 嵌入式 - 微控制器 - 特定应用 系列:- 产品变化通告:Product Discontinuation 26/Aug/2009 标准包装:250 系列:- 应用:网络处理器 核心处理器:4Kc 程序存储器类型:- 控制器系列:- RAM 容量:16K x 8 接口:以太网,UART,USB 输入/输出数:- 电源电压:1.8V, 3.3V 工作温度:- 安装类型:表面贴装 封装/外壳:208-LQFP 包装:带卷 (TR) 供应商设备封装:PG-LQFP-208 其它名称:SP000314382 |

| SL811HST-AXC | 功能描述:USB 接口集成电路 256B HOST COM RoHS:否 制造商:Cypress Semiconductor 产品:USB 2.0 数据速率: 接口类型:SPI 工作电源电压:3.15 V to 3.45 V 工作电源电流: 最大工作温度:+ 85 C 安装风格:SMD/SMT 封装 / 箱体:WLCSP-20 |

| SL811HST-AXC | 制造商:Cypress Semiconductor 功能描述:IC USB HOST CONTROLLER 48MHZ 制造商:Cypress Semiconductor 功能描述:IC, USB HOST CONTROLLER, 48MHZ 制造商:Cypress Semiconductor 功能描述:IC, USB HOST CONTROLLER, 48MHZ; No. of I/O's:8; Digital IC Case Style:TQFP; No. of Pins:48; RAM Memory Size:256KB; CPU Speed:48MHz; Peripherals:DMA; Embedded Interface Type:USB; Operating Temperature Min:0C; Operating Temperature |

发布紧急采购,3分钟左右您将得到回复。