- 您现在的位置:买卖IC网 > PDF目录297406 > SL811HS (CYPRESS SEMICONDUCTOR CORP) SL811HS Embedded USB Host/Slave Controller(SL811HS嵌入式USB主/从控制器) PDF资料下载

参数资料

| 型号: | SL811HS |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | SL811HS Embedded USB Host/Slave Controller(SL811HS嵌入式USB主/从控制器) |

| 中文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQCC28 |

| 封装: | PLASTIC, LCC-28 |

| 文件页数: | 3/32页 |

| 文件大小: | 455K |

| 代理商: | SL811HS |

第1页第2页当前第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

SL811HS

Document 38-08008 Rev. *B

Page 11 of 32

When WRITING to this register the bits definition are defined as follows.

Note: Any Write to control register 0Fh will enable the

SL811HS full features bit. This is an internal bit of the SL811HS

which enables additional features not supported by the SL11H.

For SL11H hardware backward compatibility, this register

should not be accessed.

The USB-B register set can be used when SL811HS full

feature bit is enabled.

Example. To set up host to generate 1-ms SOF time:

The register 0Fh contains the upper 6 bits of the SOF timer.

Register 0Eh contains the lower 8 bits of the SOF timer. The

timer is based on an internal 12-MHz clock and uses a counter,

which counts down to zero from an initial value. To set the timer

for 1 ms time, the register 0Eh should be loaded with value

E0h and register 0Fh (Bits 0–5) should be loaded with 2Eh. To

start the timer, bit 0 of register 05h (Control Register 1) should

be set to “1”, which enables hardware SOF generation. To load

both HIGH and LOW registers with the proper values the user

must follow this sequence:

1. Write E0h to register 0Eh. This sets the lower byte of the

SOF counter

2. Write AEh to register 0Fh, AEh will configure the part for

Full-speed (no change of polarity) Host with bits 5–0 = 2Eh

for upper portion of SOF counter.

3. Enable bit 0 in register 05h. This enables hardware gener-

ation of SOF.

4. Set the ARM bit at address 00h. This starts the SOF gen-

eration.

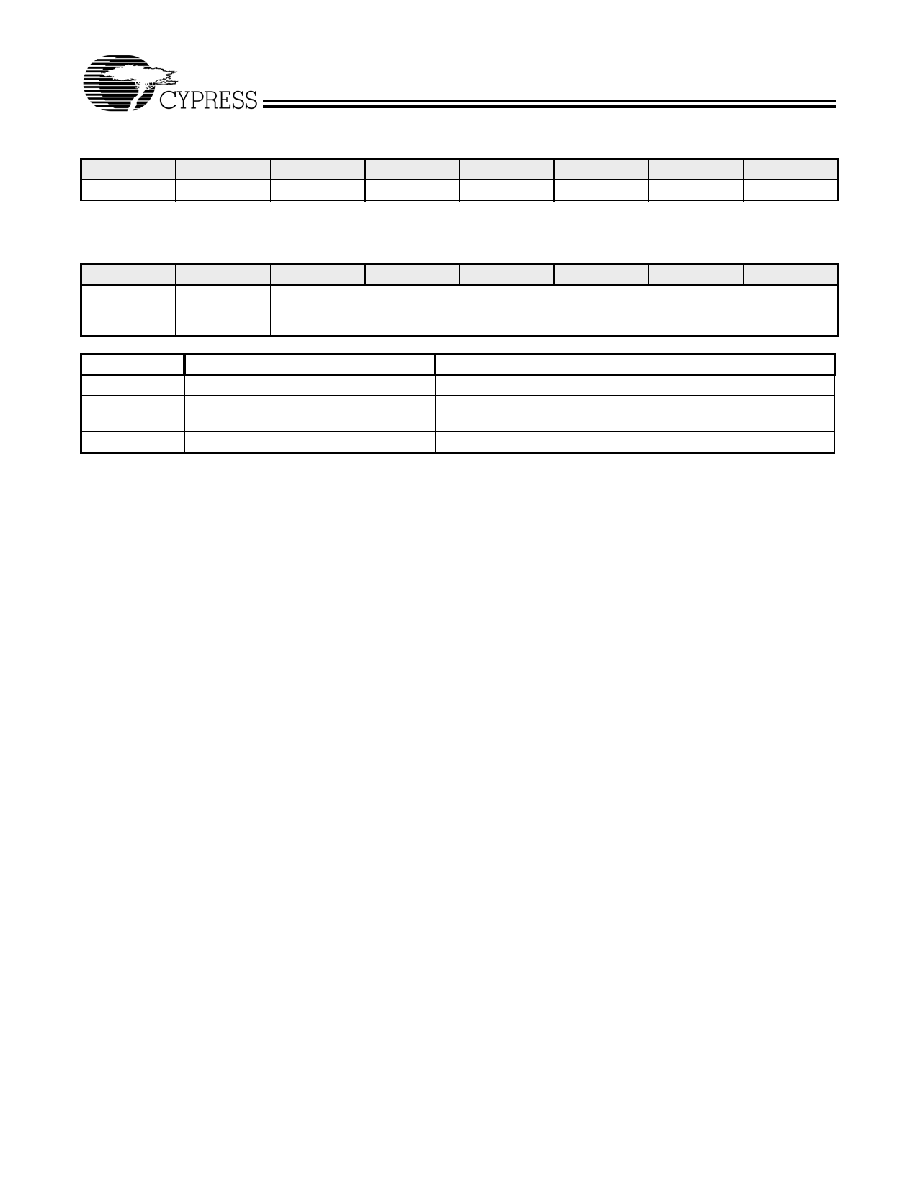

Table 3-17. SOF High Counter when READ [Address 0Fh]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

C13

C12

C11

C10

C9

C8

C7

C6

Table 3-18. Control Register 2 when WRITTEN [Address 0Fh]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SL811HS

Master/Slave

selection

SL811HS

D+/D– Data

Polarity Swap

SOF HIGH Counter Register

Bit Position

Bit Name

Function

7

SL811HS Master/Slave selection

Master = 1, Slave = 0.

6

SL811HS D+/D– Data Polarity Swap

“1” = change polarity (low-speed)

“0” = no change of polarity (full-speed).

5-0

SOF HIGH Counter Register

Write a value or read it back to SOF HIGH Counter Register.

相关PDF资料 |

PDF描述 |

|---|---|

| SLA0201 | 600 V, SCR |

| SLA24C01-D-3/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLA24C01-D/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLE24C01-S/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLE24C02-D/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SL811HS_07 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

| SL811HS_11 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

| SL811HS-DK | 制造商:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller 28-Pin PLCC |

| SL811HS-JCT | 制造商:Cypress Semiconductor 功能描述: |

| SL811HST | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

发布紧急采购,3分钟左右您将得到回复。