- 您现在的位置:买卖IC网 > PDF目录297406 > SL811HS (CYPRESS SEMICONDUCTOR CORP) SL811HS Embedded USB Host/Slave Controller(SL811HS嵌入式USB主/从控制器) PDF资料下载

参数资料

| 型号: | SL811HS |

| 厂商: | CYPRESS SEMICONDUCTOR CORP |

| 元件分类: | 总线控制器 |

| 英文描述: | SL811HS Embedded USB Host/Slave Controller(SL811HS嵌入式USB主/从控制器) |

| 中文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQCC28 |

| 封装: | PLASTIC, LCC-28 |

| 文件页数: | 8/32页 |

| 文件大小: | 455K |

| 代理商: | SL811HS |

第1页第2页第3页第4页第5页第6页第7页当前第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页第29页第30页第31页第32页

SL811HS

Document 38-08008 Rev. *B

Page 16 of 32

3.2.4.4

Interrupt Status Register, Address [0Dh]

This Read/Write register serves as an Interrupt status register when it is read, and an Interrupt clear register when it is written.

To clear an interrupt, the register must be written with the appropriate bit set to 1. Writing a 0 has no effect on the status.

3.2.4.5

Current Data Set Register, Address [0Eh]

This register indicates currently selected data set for each endpoint.

3.2.4.6

Control Register 2, Address [0Fh]

Control Register 2 is used to control if the device is configured as a master or a slave and can change the polarity of the Data+

and Data- pins to accommodate both full and low speed operation.

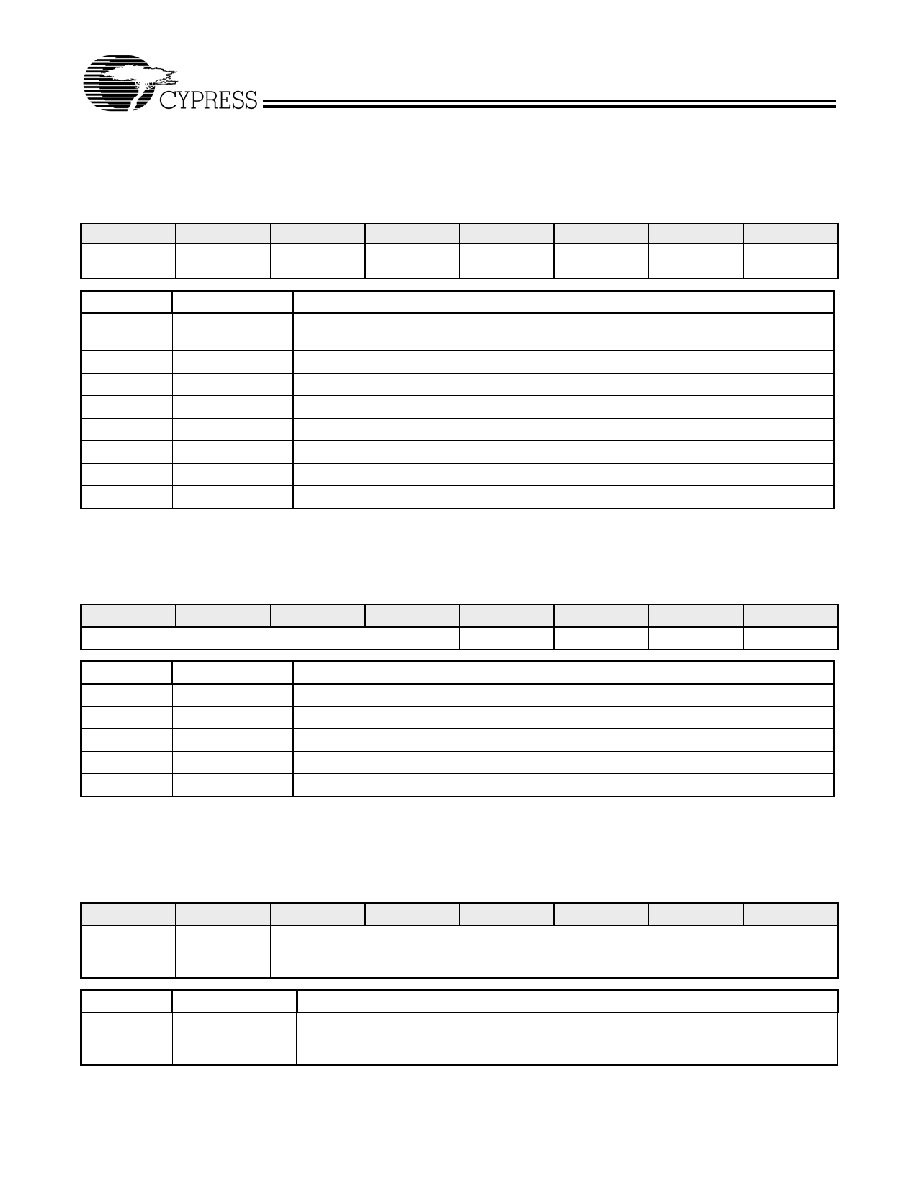

Table 3-32. Interrupt Status Register [Address 0Dh]

7

6

5

4

3

2

1

0

DMA Status

USB Reset

SOF

Received

DMA Done

Endpoint 3

Done

Endpoint 2

Done

Endpoint 1

Done

Endpoint 0

Done

Bit Position Bit Name

Function

7

DMA Status

When equal to 1, indicates DMA transfer is in progress; When equal to 0, indicates DMA

transfer is complete. An interrupt is not generated when DMA is complete.

6

USB Reset

USB Reset received interrupt.

5

SOF Received

SOF Received Interrupt.

4

DMA Done

DMA done Interrupt.

3

Endpoint 3 Done

Endpoint 3 done Interrupt.

2

Endpoint 2 Done

Endpoint 2 done Interrupt.

1

Endpoint 1 Done

Endpoint 1 done Interrupt.

0

Endpoint 0 Done

Endpoint 0 done Interrupt.

Table 3-33. Current Data Set Register [Address 0Eh]

7

6

5

4

3

2

1

0

Reserved

Endpoint 3

Endpoint 2

Endpoint 1

Endpoint 0

Bit Position Bit Name

Function

7-4

Reserved

NA.

3

Endpoint 3 Done

Endpoint 3a = 0, Endpoint 3b = 1.

2

Endpoint 2 Done

Endpoint 2a = 0, Endpoint 2b = 1.

1

Endpoint 1 Done

Endpoint 1a = 0, Endpoint 1b = 1.

0

Endpoint 0 Done

Endpoint 0a = 0, Endpoint 0b = 1.

Table 3-34. Control Register 2 [Address 0Fh]

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

SL811HS

Master/Slave

selection

SL811HS

D+/D– Data

Polarity Swap

Reserved

Bit Position

Bit Name

Function

7SL811HS

Master/Slave

selection

Master = 1

Slave = 0

相关PDF资料 |

PDF描述 |

|---|---|

| SLA0201 | 600 V, SCR |

| SLA24C01-D-3/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLA24C01-D/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLE24C01-S/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

| SLE24C02-D/P | The CAT24FC02 is a 2-kb Serial CMOS EEPROM internally organized as 256 words of 8 bits each |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SL811HS_07 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

| SL811HS_11 | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

| SL811HS-DK | 制造商:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller 28-Pin PLCC |

| SL811HS-JCT | 制造商:Cypress Semiconductor 功能描述: |

| SL811HST | 制造商:CYPRESS 制造商全称:Cypress Semiconductor 功能描述:Embedded USB Host/Slave Controller |

发布紧急采购,3分钟左右您将得到回复。