- 您现在的位置:买卖IC网 > PDF目录98091 > SN74ABT18504PMRG4 (TEXAS INSTRUMENTS INC) ABT SERIES, 20-BIT BOUNDARY SCAN REG TRANSCEIVER, TRUE OUTPUT, PQFP64 PDF资料下载

参数资料

| 型号: | SN74ABT18504PMRG4 |

| 厂商: | TEXAS INSTRUMENTS INC |

| 元件分类: | 总线收发器 |

| 英文描述: | ABT SERIES, 20-BIT BOUNDARY SCAN REG TRANSCEIVER, TRUE OUTPUT, PQFP64 |

| 封装: | GREEN, PLASTIC, LQFP-64 |

| 文件页数: | 29/32页 |

| 文件大小: | 505K |

| 代理商: | SN74ABT18504PMRG4 |

第1页第2页第3页第4页第5页第6页第7页第8页第9页第10页第11页第12页第13页第14页第15页第16页第17页第18页第19页第20页第21页第22页第23页第24页第25页第26页第27页第28页当前第29页第30页第31页第32页

SN54ABT18504, SN74ABT18504

SCAN TEST DEVICES WITH

20-BIT UNIVERSAL BUS TRANSCEIVERS

SCBS108B – AUGUST 1992 – REVISED JUNE 1993

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

6

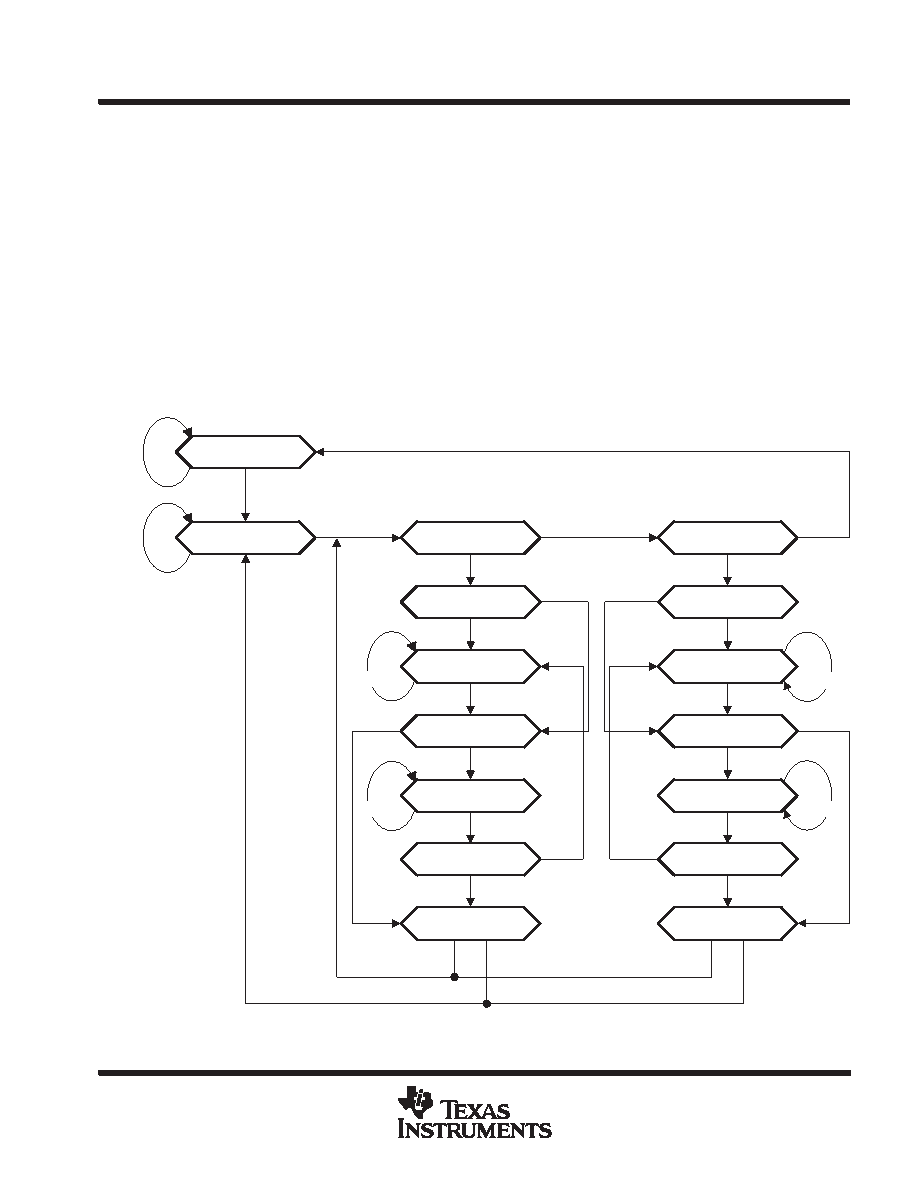

test architecture

Serial test information is conveyed by means of a 4-wire test bus or test access port (TAP), that conforms to IEEE

Standard 1149.1-1990. Test instructions, test data, and test control signals are all passed along this serial test

bus. The TAP controller monitors two signals from the test bus, namely TCK and TMS. The function of the TAP

controller is to extract the synchronization (TCK) and state control (TMS) signals from the test bus and generate

the appropriate on-chip control signals for the test structures in the device. Figure 1 shows the TAP controller

state diagram.

The TAP controller is fully synchronous to the TCK signal. Input data is captured on the rising edge of TCK and

output data changes on the falling edge of TCK. This scheme ensures that data to be captured is valid for fully

one-half of the TCK cycle.

The functional block diagram illustrates the IEEE Standard 1149.1-1990 4-wire test bus and boundary-scan

architecture and the relationship between the test bus, the TAP controller, and the test registers. As illustrated,

the device contains an 8-bit instruction register and four test data registers: an 88-bit boundary-scan register,

a 23-bit boundary-control register, a 1-bit bypass register, and a 32-bit device identification register.

Test-Logic-Reset

Run-Test/Idle

Select-DR-Scan

Capture-DR

Shift-DR

Exit1-DR

Pause-DR

Update-DR

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

Exit2-DR

Select-IR-Scan

Capture-IR

Shift-IR

Exit1-IR

Pause-IR

Update-IR

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

Exit2-IR

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

TMS = H

TMS = L

Figure 1. TAP Controller State Diagram

相关PDF资料 |

PDF描述 |

|---|---|

| SN74ABT18640DGGR | ABT SERIES, DUAL 9-BIT BOUNDARY SCAN TRANSCEIVER, INVERTED OUTPUT, PDSO56 |

| SN74ABT18640DLR | ABT SERIES, DUAL 9-BIT BOUNDARY SCAN TRANSCEIVER, INVERTED OUTPUT, PDSO56 |

| SN74ABT2240ADWRG4 | ABT SERIES, DUAL 4-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

| SN74ABT2240APWE4 | ABT SERIES, DUAL 4-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

| SN74ABT2240ADBRG4 | ABT SERIES, DUAL 4-BIT DRIVER, INVERTED OUTPUT, PDSO20 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SN74ABT18640 | 制造商:TI 制造商全称:Texas Instruments 功能描述:SCAN TEST DEVICES WITH 18-BIT INVERTING BUS TRANSCEIVERS |

| SN74ABT18640DGG | 制造商:TI 制造商全称:Texas Instruments 功能描述:SCAN TEST DEVICES WITH 18-BIT INVERTING BUS TRANSCEIVERS |

| SN74ABT18640DGGR | 功能描述:特定功能逻辑 Device w/18-Bit Inv Bus Transceiver RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74ABT18640DL | 功能描述:特定功能逻辑 Device w/18-Bit Inv Bus Transceiver RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

| SN74ABT18640DLG4 | 功能描述:特定功能逻辑 Device w/18-Bit Inv Bus Transceiver RoHS:否 制造商:Texas Instruments 产品: 系列:SN74ABTH18502A 工作电源电压:5 V 封装 / 箱体:LQFP-64 封装:Tube |

发布紧急采购,3分钟左右您将得到回复。