- 您现在的位置:买卖IC网 > PDF目录17415 > SP6133EB (Exar Corporation)EVAL BOARD FOR SP6133 PDF资料下载

参数资料

| 型号: | SP6133EB |

| 厂商: | Exar Corporation |

| 文件页数: | 13/20页 |

| 文件大小: | 0K |

| 描述: | EVAL BOARD FOR SP6133 |

| 标准包装: | 1 |

| 系列: | * |

�� �

�

�

�APPLICATION� INFORMATION�

�?� Z� (� ESR� )� =�

�?� P(LC)� =�

�ThepowerdissipationoftheSchottkydiode�

�is determined by:�

�P� DIODE� =� 2� ?� V� F� ?� I� OUT� ?� T� NOL� ?� F� S�

�where:�

�T� NOL� =� non-overlap� time� between� GH� and� GL.�

�VF� =� forward� voltage� of� the� Schottky� diode.�

�Loop� Compensation� Design�

�The� open� loop� gain� of� the� whole� system� can�

�be� divided� into� the� gain� of� the� error� ampli-�

�fier, PWM modulator, buck converter output �

�stage,� and� feedback� resistor� divider.� In� or-�

�der to cross over at the selected frequency �

�FCO� , the gain of the error amplifier has to �

�compensate� for� the� attenuation� caused� by�

�the rest of the loop at this frequency.�

�The� goal� of� loop� compensation� is� to� manipu-�

�late loop frequency response such that its �

�gain� crosses� over� 0db� at� a� slope� of� -20db/�

�dec. The first step of compensation design �

�is to pick the loop crossover frequency. High �

�crossover � frequency � is � desirable � for � fast �

�transient� response,� but� often� jeopardizes�

�the � system � stability. � Crossover � frequency �

�should� be� higher� than� the� ESR� zero� but�

�less � than � 1/5 � of � the � switching � frequency. �

�The� ESR� zero� is� contributed� by� the� ESR�

�associated� with� the� output� capacitors� and�

�can be determined by:�

� �

�2� π� ?� C� OUT� ?� R� ESR�

�The� next� step� is� to� calculate� the� complex�

�conjugate� poles� contributed� by� the� LC�

�output filter, �

� �

�2� π� ?� √� L� ?� C� OUT�

�When� the� output� capacitors� are� of� a� Ceramic�

�Type, the SP6133 Evaluation Board requires �

�a� Type� III� compensation� circuit� to� give� a� phase�

�boost of 180° in order to counteract the effects �

�of� an� under� damped� resonance� of� the� output�

�filter at the double pole frequency.�

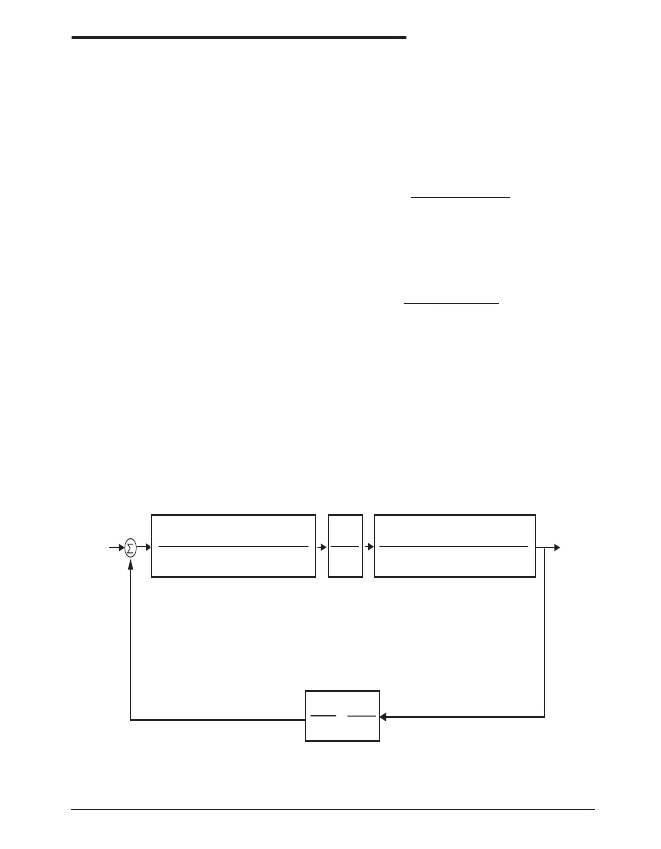

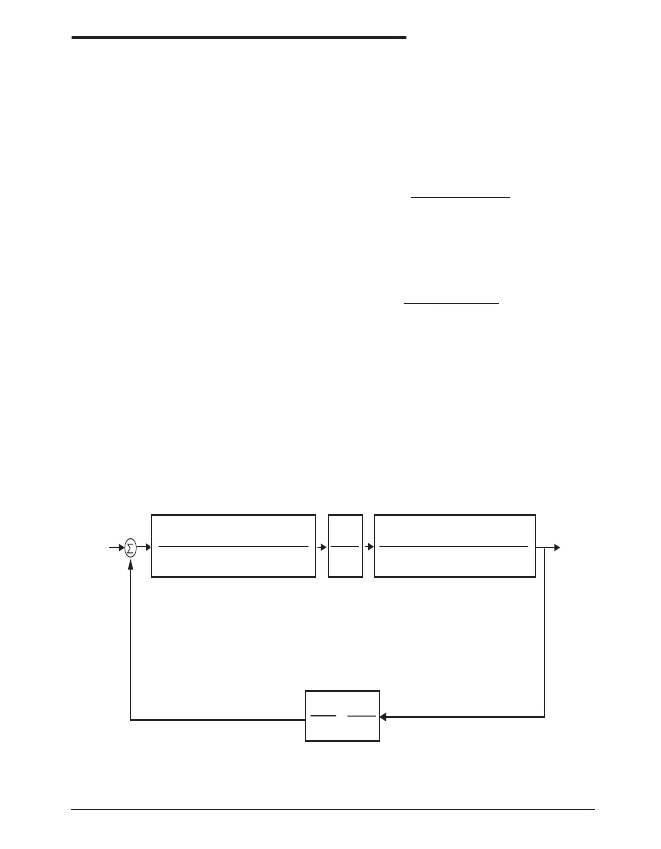

�Type� III� Voltage� Loop�

�Compensation�

�G� AMP� (s)� Gain� Block�

�PWM� Stage�

�G� PWM� Gain�

�Block�

�Output� Stage�

�G� OUT� (s)� Gain�

�Block�

�[S� LC� OUT� +S(R� ESR� +R� DC� )� C� OUT� +1]�

�V� REF�

�(Volts)�

�+�

�_�

�(SRz2Cz2+1)(SR1Cz3+1)�

�SR1Cz2(SRz3Cz3+1)(SRz2Cp1+1)�

�V� IN�

�V� RAMP_PP�

�2�

�(SR� ESR� C� OUT� +� 1)�

�V� OUT�

�(Volts)�

�Notes:� R� ESR� =� Output� Capacitor� Equivalent� Series� Resistance.�

�R� DC� =� Output� Inductor� DC� Resistance.�

�V� RAMP_PP� =� SP6132� Internal� RAMP� Amplitude� Peak� to� Peak� Voltage.�

�Condition:� Cz2� >>� Cp1� &� R1� >>� Rz3�

�Output� Load� Resistance� >>� R� ESR� &� R� DC�

�Voltage� Feedback�

�R� 2� V� REF�

�(R� 1� +� R� 2� )� V� OUT�

�Figure� 5:� SP6133� Voltage�

�Definitions:�

�Mode� Control� Loop� with�

�Loop� Dynamic�

�G� FBK� Gain� Block�

�or�

�V� FBK�

�(Volts)�

�R� ESR� = Output Capacitor Equivalent Series Resistance�

�R� DC� =� Output� Inductor� DC� Resistance�

�V� RAMP� _� PP� =� SP6 33� internal� RAMP� Amplitude� Peak� to� Peak� Voltage�

�Oct� 24-06� Rev� L�

�SP6 33� Synchronous� Buck� Controller�

� 3�

�?� 2006� Sipex� Corporation�

�相关PDF资料 |

PDF描述 |

|---|---|

| RGP02-16EHE3/54 | DIODE GPP 0.5A 1600V 300NS DO-41 |

| RS-483.3DZ/H2 | CONV DC/DC 2W 18-72VIN +/-3.3V |

| RS-4815DZ/H2 | CONV DC/DC 2W 18-72VIN +/-15VOUT |

| EL7155CSZ-T7 | IC PIN DRIVER 40MHZ 3ST 8-SOIC |

| RGP02-15EHE3/54 | DIODE GPP 0.5A 1500V 300NS DO-41 |

相关代理商/技术参数 |

参数描述 |

|---|---|

| SP6133ER1 | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:Evaluation Board Manual |

| SP6133ER1/TR | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:Synchronous Buck Controller |

| SP6133ER1-L | 功能描述:DC/DC 开关控制器 Synchronous Buck Controller RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| SP6133ER1-L/TR | 功能描述:DC/DC 开关控制器 Synchronous Controller RoHS:否 制造商:Texas Instruments 输入电压:6 V to 100 V 开关频率: 输出电压:1.215 V to 80 V 输出电流:3.5 A 输出端数量:1 最大工作温度:+ 125 C 安装风格: 封装 / 箱体:CPAK |

| SP6134 | 制造商:SIPEX 制造商全称:Sipex Corporation 功能描述:Dual Supply Synchronous Buck Controller |

发布紧急采购,3分钟左右您将得到回复。